直到70年代末,未充分開發的毫米波(mmWave)頻率范圍(30至300ghz)僅限于小范圍應用,如光譜學和軍用雷達。前端的復雜性和對非標準制造技術的需求使得毫米波模塊的成本無法滿足大批量和消費市場的需求。自80年代初以來,研發機構展示了重大進展,并在半導體行業取得了進展,為廣泛的應用開辟了新的領域:高數據率通信、汽車雷達、機載和導彈跟蹤系統、空間光譜分析和成像。據估計,2013年,mmWave組件市場的全球收入約為1.16億美元,預計到2018年將達到11億美元,復合年增長率(CAGR)約為59%。2雖然業界認為這是一個巨大的經濟機遇,但新興應用正在帶來具體的挑戰在電氣性能、緊湊性、集成可能性和系統可靠性方面。本文重點介紹中短程通信設備,這些設備說明了與無線收發器的集成及其與其他組件共存相關的一些技術挑戰。毫米波頻率下的短波長可以看作是集成無源元件的機會,這些元件的典型尺寸與標準電子封裝兼容。在某些應用中,諸如波導管、連接器、非平面濾波器和大型天線陣列等體積龐大的元件仍然阻礙著向完全集成和小型化系統發展。就短程、60GHz通信而言,便攜式設備有望成為未來十年的主要市場驅動力,因此需要完全集成、緊湊且高性能的收發器。關于天線,小型化過程受到散熱器面積和可實現增益之間的基本關系的限制;這通常被視為無線收發器完全集成的瓶頸。

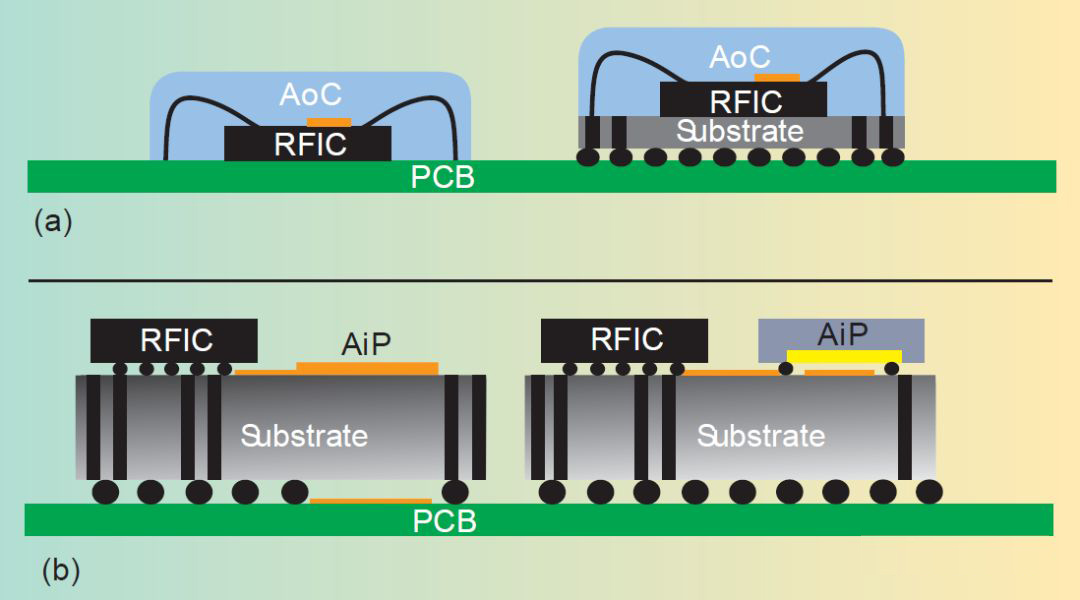

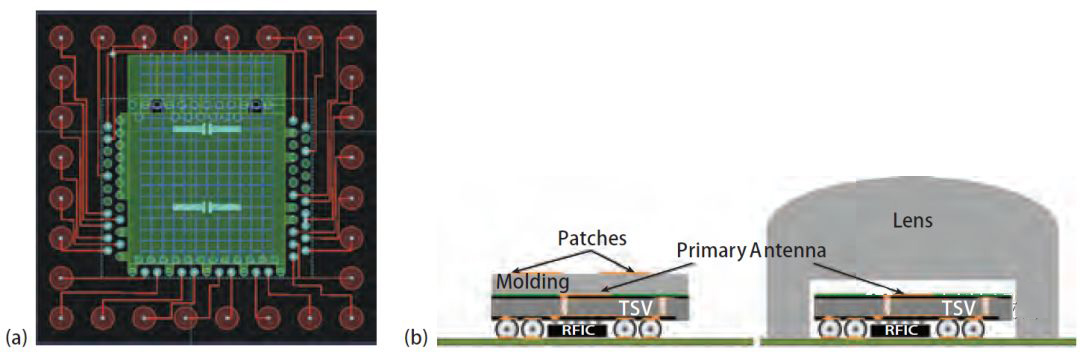

片上天線(AoC)方法包括將輻射元件直接集成到射頻集成電路芯片的后端堆棧中,無論是采用CMOS、BiCMOS還是III-V工藝制造(見圖1a)。這種解決方案的主要優點在于無需任何射頻互連,并且所有射頻和基帶功能都可以在一個幾平方毫米大小的模塊上進行聯合集成。然而,對于硅基AoCs,襯底的高介電常數(εr=11.7~11.9)和低電阻率(t~10Ω?cm)嚴重降低了匹配帶寬和輻射效率。盡管如此,AoC天線的特性仍然可以通過局部地改變襯底的特性來改善。例如,可以通過蝕刻輻射元件下方的空腔或實現懸浮膜來實現。在這兩種情況下,空氣層的存在使介電損耗最小化,并降低有效介電常數。其他創新的解決方案包括使用離子注入工藝或上述耦合輻射元件的集成對硅襯底電阻率進行局部修改。

圖1 AoC(a)和AiP(b)集成方案。

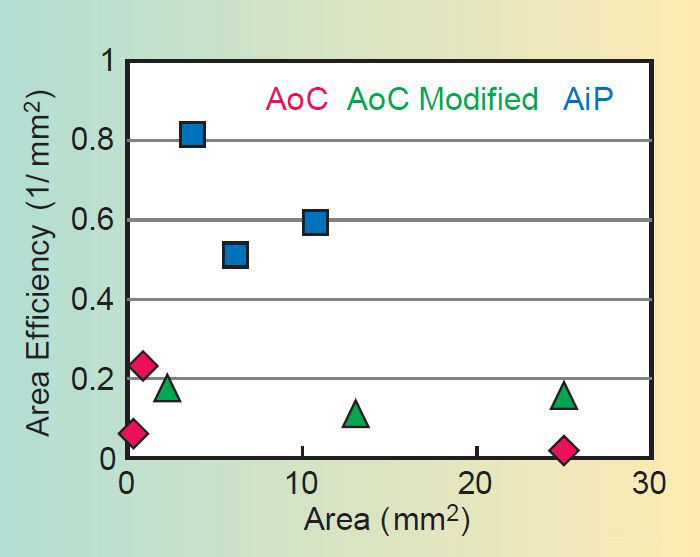

在天線封裝(AiP)集成方法中,天線在獨立于RFIC芯片的獨立襯底上實現(見圖1b)。該基板既可以專門用于輻射元件及其饋電線路,也可以作為收發組件和異構集成的封裝。因此,AiP設計在mmWave收發器的3D集成方案中起著關鍵作用,同時提供了選擇低介電常數和/或高電阻率襯底的額外自由度。另外,天線允許的面積比舞臺允許的大。因此,綜合天線性能比較的一個有效基礎應該考慮到分配的面積,并且我們可以定義一個新的優點系數來歸一化單位面積的實現增益(線性尺度)。圖2描繪了60ghz集成天線的文獻調查,表明由于使用低損耗襯底而不是CMOS級硅,aip的增益是aoc的2到4倍。

圖2集成天線的典型面積效率。

為無線收發器的集成選擇一種給定的技術是在幾個限制條件之間的權衡:電氣性能、熱機械可靠性、緊湊性、可制造性和成本。今天的高密度互連(HDI)設計規則繼承了成熟成熟的PCB技術,允許線和間隙小于40μm,以及直徑小于100μm的微通孔形成,這符合毫米波集成的要求。此外,新一代多層有機(MLO)封裝在薄膜和厚膜結構中都使用高質量的電介質。因此,標準的FR-4芯和重分布層層板正逐漸被低損耗的介質(如RO系列和液晶聚合物(LCP))所取代。例如,意法半導體公司利用一種基于RO4003C核對稱疊加的技術,開發了一種60GHz、HDI、有機封裝

在同樣的背景下,陶瓷封裝由于其化學穩定性、機械可靠性和密封裝配的特性,在大約二十年前被引入以滿足關鍵系統的需要。陶瓷加工允許創建各種通孔和腔體結構以及外部電容器和電感器的組裝。標準多層陶瓷封裝的垂直分辨率約為50μm。目前使用的兩種主要多層陶瓷工藝是低溫共燒陶瓷(LTCC)和高溫共燒陶瓷(HTCC),最大共燒溫度分別約為900°C和1600°C。雖然HTCC工藝為封裝提供了很大的物理穩定性,但只有高熔點金屬,如鎢(Tf=3422°C)和鉬(Tf=2623°C)可用于內層布線。不幸的是,與LTCC的銅、鈦/金合金或銀金屬化相比,這些金屬的導電率相對較低(分別為8.9×106和18.7×106 S/m),后者在高頻下具有較低的導電損耗。在文獻中可以找到來自業界的一些令人信服的貢獻,例如IBM的60GHz LTCC模塊以及MLO包(RO4000和LCP)

作為發展最快的封裝技術之一,嵌入式晶圓級球柵陣列(eWLB)是一種結合了先進的再分配層處理和晶圓到模具轉移技術的晶圓級封裝方法。一個保護風扇的布線和保護聚合物的雙重作用。eWLB工藝(包括凸點下金屬化)繼承自硅微制造線。由于使用了低應力模塑聚合物,eWLB封裝可適用于具有天線陣列的大型封裝,同時確保線/空間臨界尺寸約為15μm。文獻中可找到幾種集成天線的毫米波封裝演示,其中重點介紹了Linz演示的雷達應用University and DICE GmbH.6,7這項最新技術為3D集成提供了很有前景的前景,這得益于采用貫穿封裝互連的封裝對封裝(PoP)組裝的可能性。

今天的硅后端生產線提供了一個大面板的微制造技術,以實現系統封裝(SiP),如微機械加工,光刻,離子和激光蝕刻,以及一個大面板的沉積和層壓技術。標準硅工藝可以很容易地達到微米級的分辨率,滿足毫米波甚至亞太赫茲系統的要求。在過去的五年中,有機和硅插入器封裝已經被ASIC和存儲器應用所普及,但是最近的異構集成趨勢顯示出射頻功能的更多展示以及玻璃作為高頻應用的潛在候選的引入。

如前所述,硅微制造特別適合于毫米波應用,因為它具有成熟和標準的后端工藝的無與倫比的分辨率。與陶瓷(σ<20 W?m-1?K-1)和PCB材料(σ<1 W?m-1?K-1)相比,硅封裝具有優異的導熱性(25°C時σ~150 W?m-1?K-1),這在外部功率放大器與收發器芯片組裝的典型場景中非常重要。

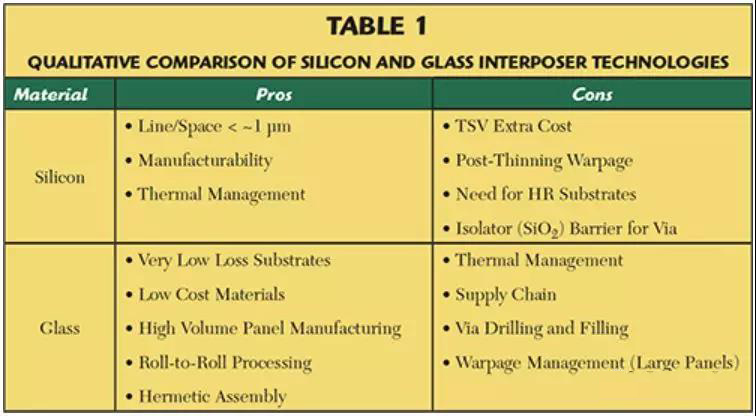

近年來,人們對2.5D和3D玻璃中間層及其提供的新的集成機會產生了越來越多的興趣。玻璃基片具有優良的介電性能,具有低介電常數(εr~4~6,取決于成分和工藝)和低損耗正切值,是射頻封裝和無源器件集成的理想材料。表1比較了玻璃和硅中間層。用大面板代替晶圓有利于大規模生產,而在穿透玻璃通孔(TGV)鉆孔和填充以及再分配層(RDL)處理方面取得了重大進展。今天的玻璃中介機構專責小組由朝日、康寧玻璃和3D玻璃解決方案等制造商和供應商以及領導國際中介機構財團的喬治亞理工學院等學術研究機構組成。然而,玻璃面板和加工設備的供應鏈并沒有像硅、有機、陶瓷和eWLB技術那樣得到很好的定義。隨著下一代3D集成設備的出現,2.5D/3D玻璃插入器技術更可能達到完全成熟;目前,它足以滿足高性能計算和數據中心等利基應用,在這些應用中,對成本的關注較少。8

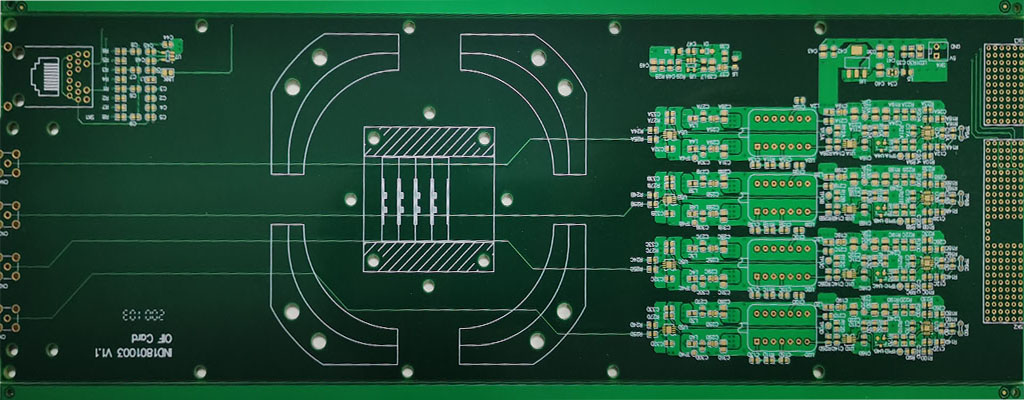

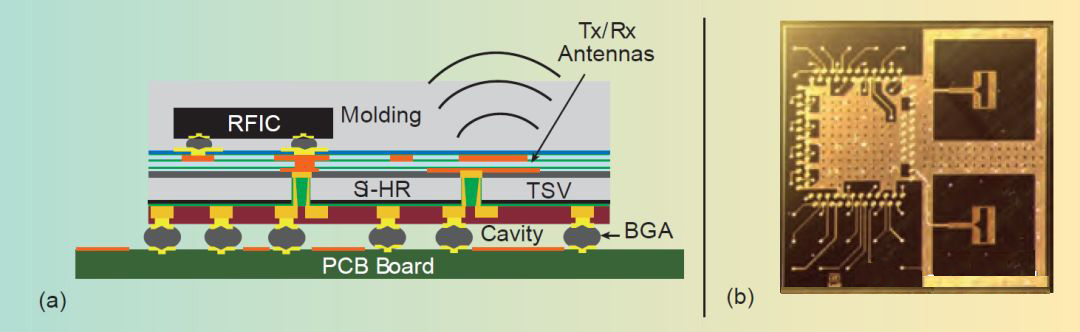

圖3 60 GHz模塊(a)的橫截面示意圖和硅插入器芯片(b)的顯微照片。

CEA-Leti開發的第一個全功能插入器封裝基于高電阻率(ρ>1 kΩ?cm)、120μm厚的硅襯底,具有兩個正面和一個背面銅再分配層。插入器的每一側分別帶有所使用的凸點下金屬化,對于射頻集成電路倒裝芯片(使用銅柱或微凸點)和使用球柵陣列(BGA)焊料球在主PCB板上組裝封裝。9插入器芯片的兩側使用直徑為60μm(縱橫比為2:1)的充銅穿透硅通孔(TSV)互連連接。插入器的總面積為6.5 mm×6.5 mm,是迄今為止報道的具有集成天線的最緊湊的60 GHz收發器。圖3a顯示了模塊的未標度橫截面以及用于確保組件完整性的插入器、射頻集成電路芯片和成型聚合物。60ghz射頻集成電路收發機采用65nmcmos工藝制造,兩個折疊偶極子天線(用于發射和接收)位于前端的上部RDL層。由銅帶和TSV陣列構成的保護環用于減輕兩個背腔天線之間的表面波耦合(見圖3b)。

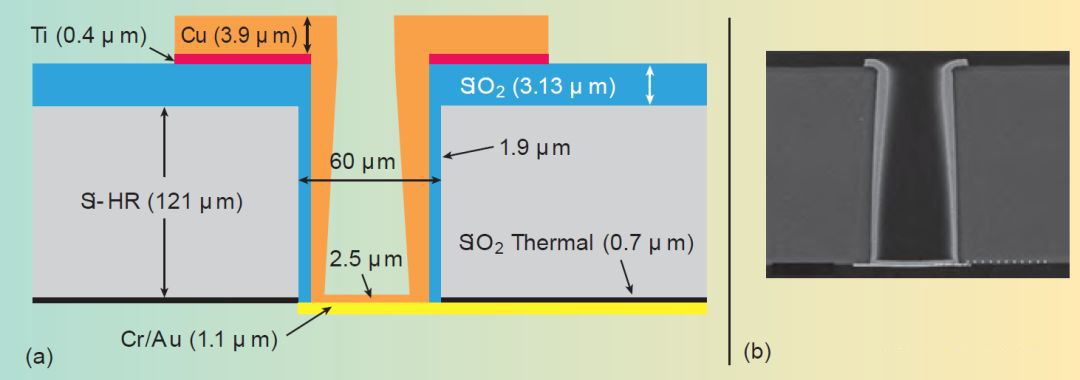

圖4 TSV鞋楦橫截面示意圖(a)和SEM視圖(b)。

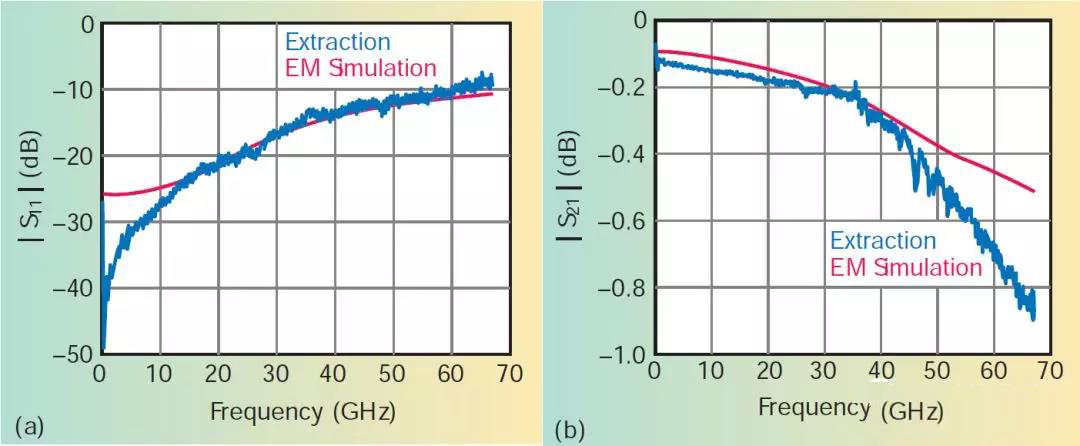

這個模塊是一個典型的2.5D集成方案的演示,其中射頻集成電路組裝在插入器的頂部,并與天線偏移放置。垂直互連是通過最后一個過程使用Leti的定制TSV實現的。圖4顯示了TSV的橫截面和SEM圖像。雖然收發機中TSV互連的主要功能是驅動低頻和基帶信號,但測試車輛包含了額外的測試功能,以通過封裝布線和背面天線饋電來研究它們對mmWave的適用性。已經使用射頻探針測量和適當的去嵌入技術研究了TSV的電氣性能,以提取單個GSG躍遷在直流至67 GHz的寬帶響應。11躍遷在60 GHz時顯示約0.6 dB的插入損耗,50Ω終端的阻抗失配是主要因素,i、 e.,0.46 dB(見圖5)。除了寬帶特性外,基帶信號完整性還通過頻域響應的傅里葉逆變換進行了研究。用5gbps偽隨機二元序列(PRBS)進行的瞬態眼圖分析顯示,眼開度為96%。

圖5 GSG配置中50Ω端接TSV過渡的反射(a)和傳輸(b)。

Leti正在進行的研究旨在創造新一代的毫米波插入器封裝,與其他競爭技術相比,具有更好的電氣和機械性能、合理的成本和可制造性。目前正在進行布局和預制分析的新模塊與第一個演示器保持相同的總厚度;但是,由于集成的高阻抗表面(HIS)反射器設計(見圖6a),總面積減少了約33%(從6.5 mm×6.5 mm降至5.3 mm×5.3 mm)。12正在評估兩種改進方案,以提高天線性能,如圖6b所示,第一個步驟是在插入器頂部層壓成型聚合物,并處理金屬寄生貼片以提高帶寬。第二個目標是通過外部介質透鏡提供中程通信能力(大約10米)。在這種情況下,60ghz的目標增益是15dbi。建議的透鏡設計基于半球形和拋物線幾何形狀,采用PA6級機加工塑料(εr=4.3)。四種設計中的兩種,直徑為6毫米和1厘米的半球形透鏡,已經過實驗驗證。第一次測量使用了一個開放的WR15波導饋源,在57到66GHz范圍內顯示出12到16dBi的增益。在系統級驗證工作流程之后,這些透鏡已與60 GHz QFN收發器模塊13共同集成,并證明了一個發射透鏡的范圍提高了四倍,發射和接收透鏡的范圍提高了7.5倍

圖6由A.Moknache(A)和基于HIS天線的新3D集成方案(b)提供的3D中間層簡化布局。