導電膠分層作為封裝失去效力問題,一直遭受廣泛的關心注視。基于

ANSYS

平臺,對導電膠脫落應力仿真,用來評估導電膠在封裝和測試過程中分層風險,共進一步剖析了頂部芯片、絕緣膠厚度以及導電膠厚度對導電膠分層的影響。最后結果表明:

導電膠在靠得住性測試階段 125

℃冷卻到室溫階段最容易發生導電膠分層失去效力。該款封裝中導電膠分層的端由是頂部疊層芯片結構引動的。經過對頂部芯片、絕緣膠的厚度施行預設,發覺其厚度越薄導電膠的脫落應力越小,分層風險越小。導電膠的厚度在

10 μm 時,膠體的粘貼力最大,脫落應力最小,導電膠分層風險最小。

隨著電子工業對背景盡力照顧要求不斷增長,傳統封裝中運用鉛焊料污染背景,逐漸被環保導電膠接替。但導電膠的熱體脹系數與芯片相差較大,在溫變負荷下容易萌生熱應力使導電膠分層。一朝導電膠分層嚴重將導致芯片功能失去效力。針對導電膠分層國里外學者施行了廣泛的研究討論和研討。龍平覺得導電膠分層主要是因為熱負荷下各局部膨脹和收縮不均引動的。Sujan

等對銀膠剪切熱失配雙層板型的剖析表明,隨著剪切力增大,導電膠分層程度減小。國內學者經過

ANSYS軟件剖析導電膠的熱應力,研討基板厚度對導電膠最大熱應力的影響,并提出封裝結構優化的處理辦法,隨著基板厚度的增加,導電膠最大熱應力先減小后增大,在基板厚度為

4~5 mm

時最小,導電膠分層現象有所改善。海外學者利用熱循環后導電膠的群體等效應力并接合芯片剪切合實際驗評估導電膠分層風險,但僅只減小等效應力最大值很難改善導電膠分層。固然利用有限元法剖析導電膠熱應力是一種管用手眼,但僅剖析群體熱應力最后結果并不可以直接評估導電膠與芯片界面分層風險。本文基于有限元法剖析導電膠的脫落應力,直接評估導電膠與芯片界面分層(導電膠分層)風險,減小導電膠分層。經過仿真最后結果剖析導電膠失去效力階段及端由,并施行封裝內里結構預設,改善導電膠分層。

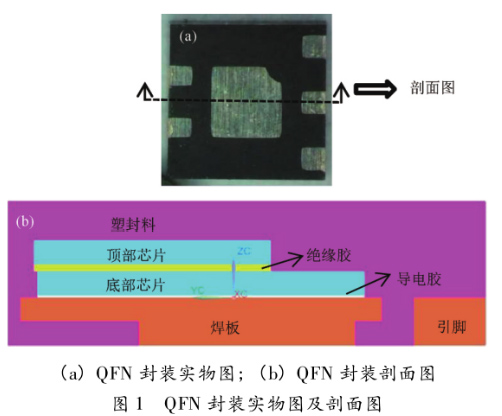

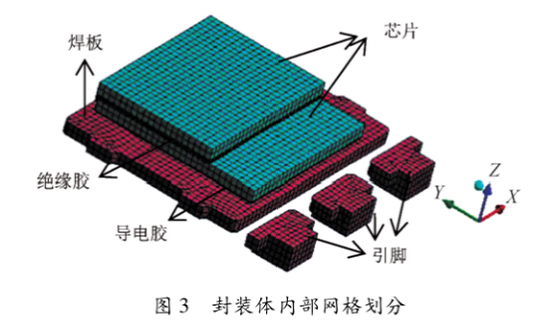

封裝體由芯片、導電膠、絕緣膠、焊板及引腳、塑封料想到金線構成,如圖

1 所示。金線對導電膠分層影響細小,故建模時可以疏忽。封裝體尺寸為 2. 0mm×2. 0 mm×0. 6 mm,頂部芯片尺寸為 1. 37 mm×1mm×0.

12 mm,絕緣膠尺寸為 1. 37 mm×1 mm×0. 04mm,底部芯片尺寸為 1. 37 mm×1. 35 mm×0. 12 mm,導電膠尺寸為 1.

37 mm×1. 35 mm×0. 01 mm。

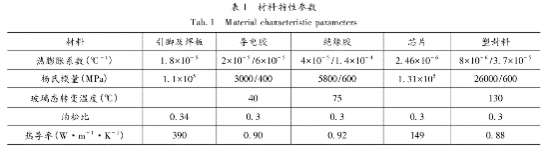

導電膠運用 Henkel 企業的 QMI519,塑封料運用 Nitto 企業 G770HCD,材料特別的性質參變量如表1 所示。導電膠和塑封料的熱體脹系數(CTE)和楊氏模量(E)在玻璃態轉變溫度 T g 近旁激變。2×10-5/6×10-5和 3000/400 表達當溫度低于 T g 時,導電膠CTE 和 E 的值作別為 2×10- 5℃-1和 3000 MPa,當溫度高于 T g 時,CTE 和 E 作別取 6×10-5℃-1和 400MPa。同理塑封料也具備此類性質。

粘接界面的靠得住性由界面的粘貼力和內部策應力的體積表決。導電膠的粘貼力與本高矮胖瘦料相關。內部策應力由熱應力和濕應力組成。QMI519

導電膠吸濕性很低,外部塑封料盡力照顧使潮氣很難進入境內導電膠內里,故導電膠的濕應力較小。

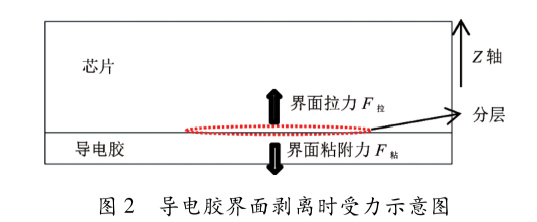

芯片在封裝過程中經歷復雜溫度變動,導電膠必然性萌生熱應力。熱應力中與界面脫落有關的應力稱作脫落應力。脫落應力分為拉應力和壓應力,但只有拉應力才有界面脫落風險,拉應力越大則材料之間越容易產疏遠層。因為這個,當導電膠材料未變事情狀況下,可以用脫落應力體積評估導電膠分層風險。圖 2 為導電膠界面脫落時受力概況圖,界面張力是界面分層影響主要因素。

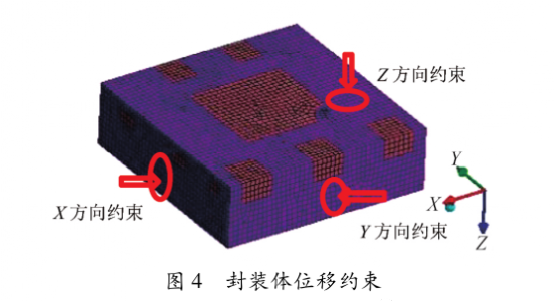

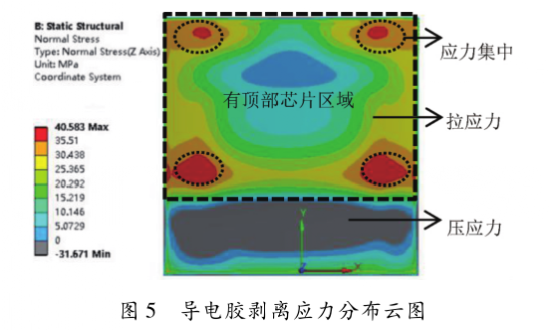

ANSYS 軟件施行導電膠脫落應力仿真。圖 3是封裝體內里網格圖,網格單元為 39964,節點數量為 191617。熱剖析時室溫為 25 ℃,參照溫度為起初溫度,參照溫度時為零應力狀況,用于計算導電膠的熱應力。同時設置空氣天然對流,焊板底部設置溫度負荷,時間為 2400 s。靜應力板塊剖析時,設置底面為 Z 方向位移約束,左、面前為 X、Y 方向位移約束,如圖 4 所示。導電膠在125 ℃冷卻到室溫時脫落應力如圖 5 所示,導電膠有頂部芯片地區范圍均為拉應力,同時該地區范圍顯露出來四個應力集中地區范圍,而無頂部芯片地區范圍大多為壓應力,開始階段的推斷頂部疊層芯片結構對導電膠脫落應力萌生影響。

芯片封裝要通過很多的工藝流程譬如貼片、塑封等。導電膠分層有關過程涵蓋:

導電膠固化175 ℃ 冷卻到室溫過程; 塑封后固化時從室溫加熱至 175 ℃ 過 程; 塑 封 后 固 化 175 ℃ 冷 卻 至室溫。

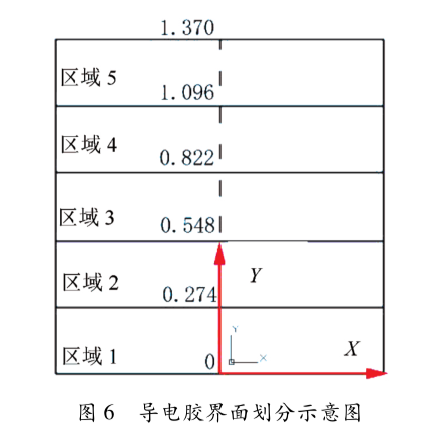

從圖

5 可知導電膠外表脫落應力云圖關于 Y 軸對稱,將云圖沿 Y 軸區分清楚 5 個地區范圍比沿 X 軸更能反映脫落應力散布,區分清楚地區范圍概況圖如圖 6

所示。將導電膠脫落應力云圖導出數值作別計算出各地區范圍脫落應力均值,并畫出以 Y 軸距離為橫坐標的曲線圖。

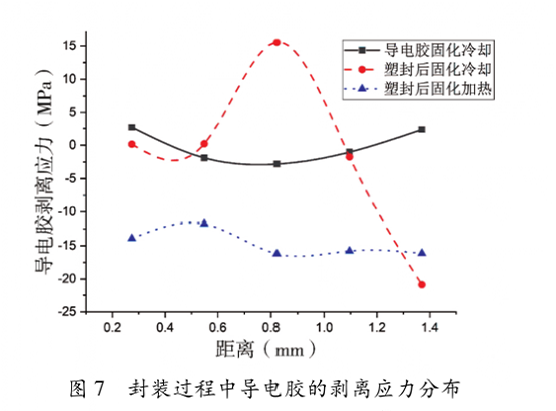

封裝過程中導電膠脫落應力散布如圖 7 所示,塑封后固化 175 ℃ 冷卻至室溫過程,脫落應力達到 15 MPa,在芯片封裝過程中分層風險最大。導電膠固化冷卻過程中拉應力較小,脫落風險較小。

塑封體不可少通過靠得住性測試,其目標為檢驗測定在產品運用時是否容易出毛病、產品運用生存的年限是否合理等。基于

J-STD-020 標準施行 MSL 嘗試,首先125 ℃烘烤 24 h,再于 85 ℃濕熱 168 h,最終行260 ℃回流焊。

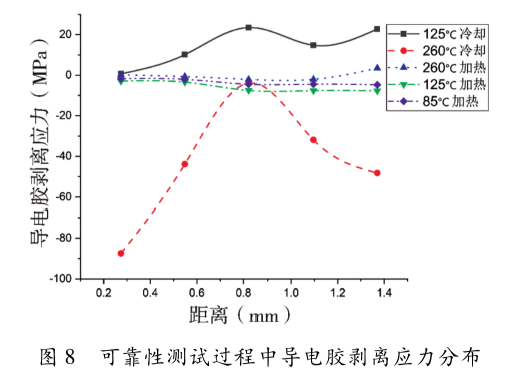

靠得住性測試各過程導電膠脫落應力散布如圖 8所示,125 ℃ 冷卻到室溫時導電膠脫落應力最大,脫落應力均為拉應力。回流過程中,85 ℃ 加熱到260 ℃導電膠拉應力較小,260 ℃ 冷卻到室溫時拉應力地區范圍表面化較小,壓應力表面化增大,但壓應力并不是造成導電膠分層的端由。可見,并不是溫度越高導電膠越容易分層。

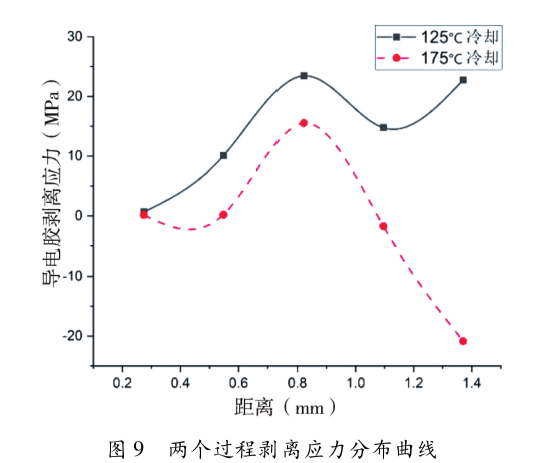

塑封后固化

175 ℃冷卻過程和 125 ℃冷卻過程作別是封裝過程和靠得住性測試過程脫落應力最大的過程。經過將兩個過程施行比較,得出 125

℃冷卻過程導電膠的脫落應力更大,拉應力地區范圍更多,界面脫落的風險更大,如圖 9 所示。因為這個,導電膠分層最易發生在 125

℃冷卻過程中。

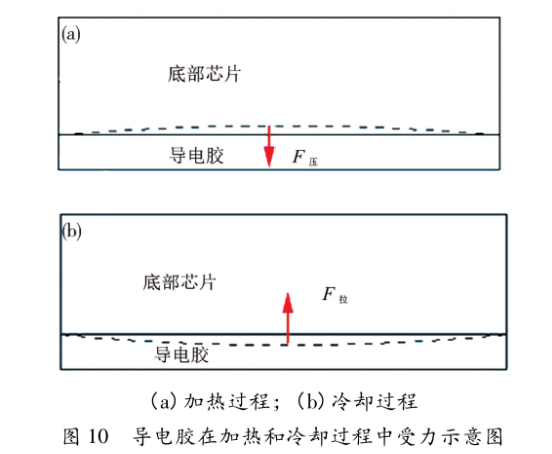

導電膠的熱體脹系數(CTE)比芯片大,若不思索問題封裝體結構的影響等因素,加熱時導電膠向外膨脹,Z 方向變型量是大于零的。同理,冷卻過程中導電膠材料向內里收縮,Z 方向變型量是小于零的。圖 10(a)表達導電膠在加熱過程中受力概況圖,芯片遭受導電膠材料的擠壓會對導電膠萌生一個壓應力。因為這個,加熱過程導電膠基本上都是壓應力,導電膠分層風險小。圖 10(b)表達冷卻過程中導電膠的受力概況圖,芯片對導電膠有個拉應力,故導電膠在冷卻過程中有較大地區范圍的拉應力散布,導電膠分層風險大。

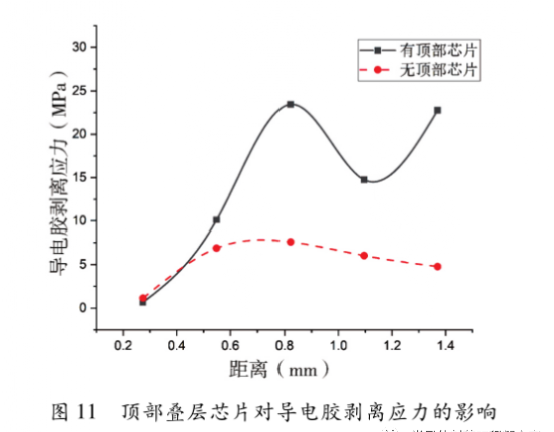

除開溫度負荷對導電膠的分層影響,封裝體結構也會對導電膠分層有影響。開始階段的推斷該 QFN 封裝導電膠分層是因為頂部芯片疊層引動的。通不為己甚析導電膠脫落應力云圖,在 125 ℃冷卻至室溫時有頂部疊層芯片地區范圍使導電膠脫落應力增加很多。經過有/無頂部芯片仿真數值剖析,頂部疊層芯片結構的確增加了導電膠脫落應力,如圖 11 所示。

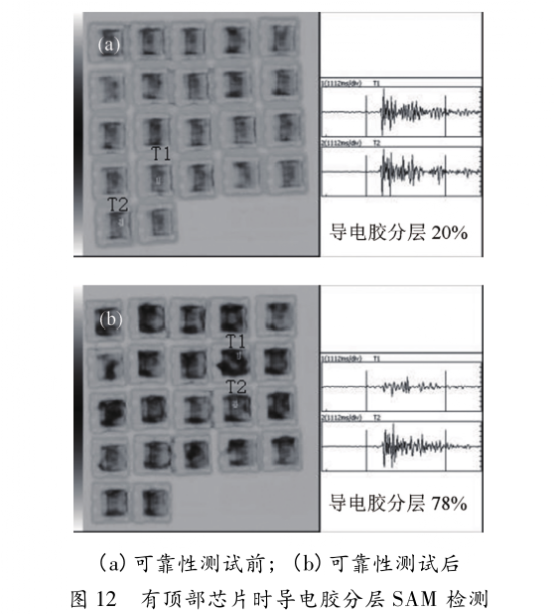

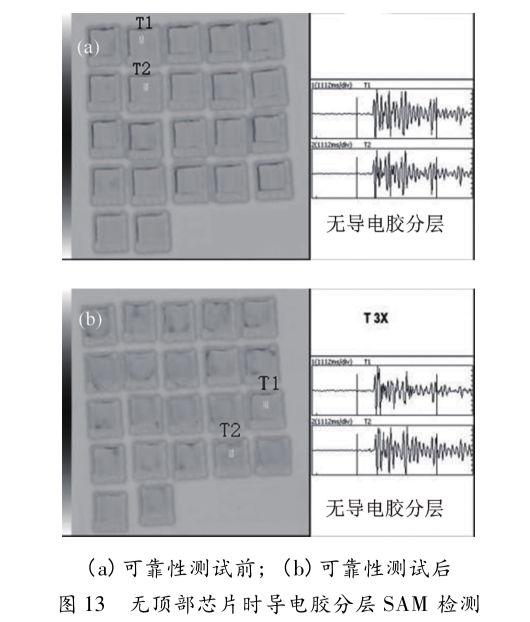

到現在為止,大部分數企業經過超引起聽覺的振動波電子掃描目鏡(SAM)仔細查看導電膠分層事情狀況。因為導電膠分層容易發生在靠得住性測試的過程中,故在靠得住性測試前后作別施行 SAM 測試。從圖 12 看出有頂部芯片結構封裝中導電膠在靠得住性測試前后均發疏遠層現象,但在靠得住性測試后導電膠發疏遠層程度更大,分層地區范圍達到 78百分之百。圖 13 是無頂部芯片結構封裝中導電膠 SAM 圖,導電膠在靠得住性測試前后均未發疏遠層。因為這個,該款封裝中導電膠分層失去效力是因為頂部疊層芯片引動的。

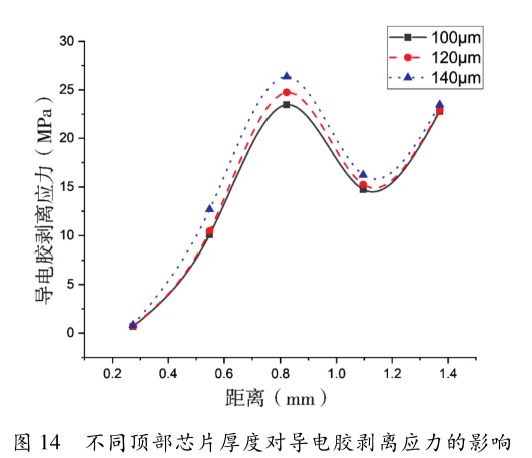

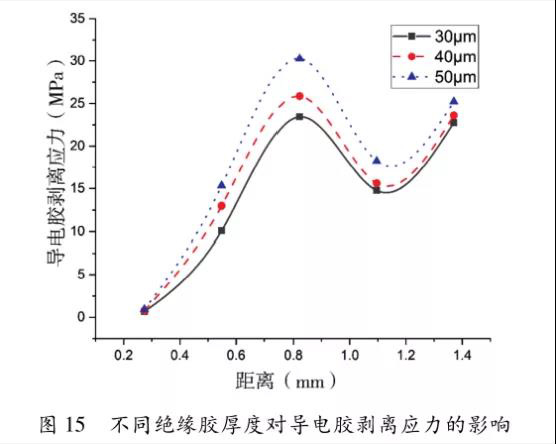

因為頂部疊層芯片結構是導致導電膠分層失去效力的端由,所以基于脫落應力仿真對封裝體結構施行優化預設。首先對頂部芯片以及絕緣膠的厚度預設,頂部芯片厚度 100~140 μm。絕緣膠厚度 30~50 μm。在 125 ℃冷卻至室溫過程中施行脫落應力仿真。

導電膠的脫落應力隨著頂部芯片厚度減小而減退,頂部芯片厚度為 100 μm 時導電膠脫落應力最小,如圖 14 所示。當絕緣膠厚度為 30 μm 時,導電膠脫落應力最小,且絕緣膠厚度越小,導電膠脫落應力越小,如圖 15 所示。

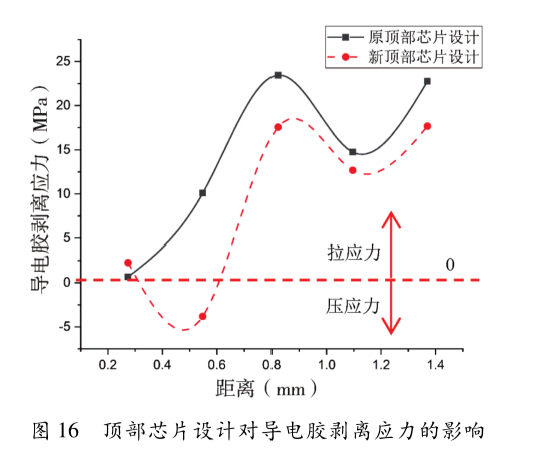

從圖 5 看出導電膠的脫落應力有可能與頂部疊層芯片的平面或物體表面的大小相關。為此,對頂部芯片的體積預設,將芯片的尺寸減小至 1. 07 mm×0. 8 mm×0. 1 mm。將新預設的封裝施行仿真,新預設頂部芯片尺寸要得導電膠的脫落應力減小,拉應力散布減小,如圖16 所示。因為這個,減小頂部芯片的平面或物體表面的大小能夠改善導電膠分層現象。

電膠厚度的預設導電膠的厚度變動不止變更脫落應力體積,并且會影響膠體的粘貼力。

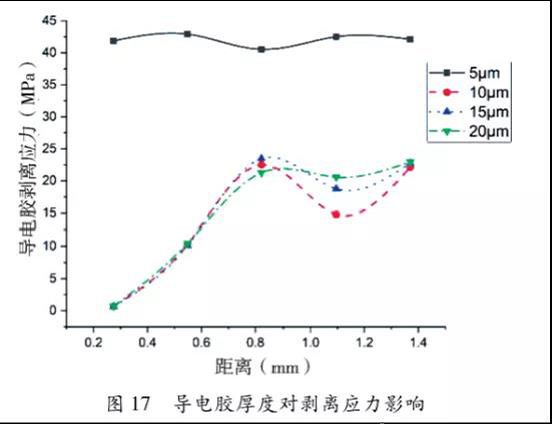

圖

17 表達不一樣厚度導電膠的脫落應力,導電膠厚度為 10 μm 時,其脫落應力較其它厚度時要小。但并非導電膠厚度越小越好,當厚度減至 5μm

時,導電膠的脫落應力迅疾增大,容易導致導電膠分層失去效力。當厚度超過 10 μm 時,導電膠脫落應力隨著厚度增加而增大。

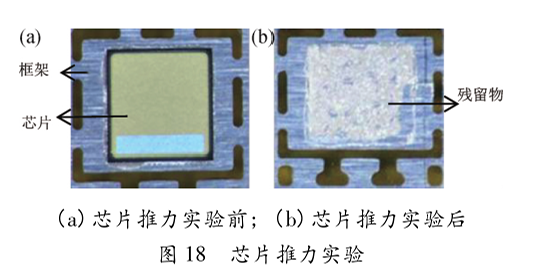

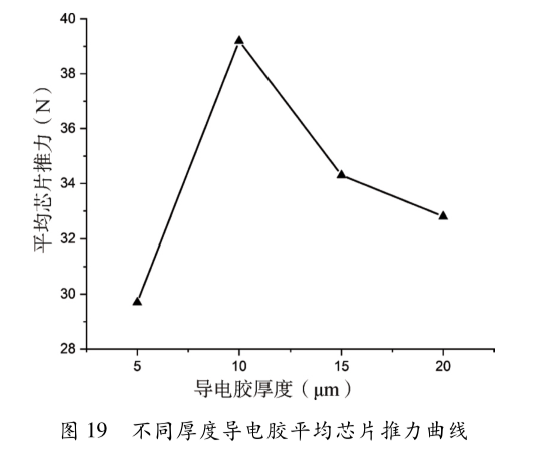

導電膠的厚度變更時,膠體對芯片粘貼力變樣。經過芯片推力測試儀對固化后導電膠施行芯片推力實驗,用芯片推力來表征導電膠對芯片的粘貼力體積,芯片推力越大則導電膠粘貼力越大。每種導電膠厚度選出 10 組,共 40 組施行芯片推力實驗,再算出每種厚度導電膠均勻芯片推力值以減小實驗誤差。圖 18 表達芯片推力實驗,在框架上遺留物越多表達芯片推力越大。圖 19 表達不一樣導電膠厚度時的均勻芯片推力體積,導電膠厚度為 10μm 時芯片均勻推力最大,表征導電膠對芯片粘貼力也最大,群體上芯片推力隨著導電膠厚度的增加先增大,當厚度超過 10 μm 時一直減小。導電膠厚度為 5 μm 時,導電膠過薄造成粘貼力不充足。一方面是界面起粘貼效用的物理及化學鍵減損引動的,另一方面膠體本身機械強度低,在芯片推力實驗中容易萌生粘結毀傷。從圖 17 和圖 19 可知增加導電膠厚度并不可以改善導電膠的脫落應力,反倒減小了導電膠對芯片的粘貼力,增加了導電膠分層的風險。同時增加導電膠厚度導致導電膠耗費,經濟性較差。

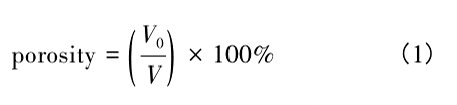

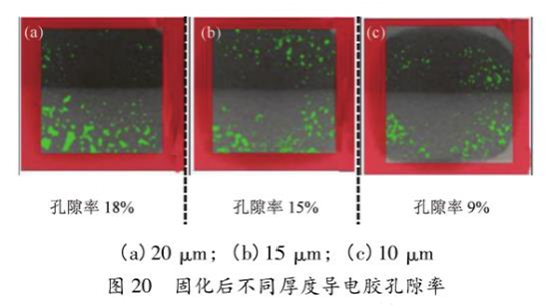

當導電膠厚度大于 10 μm 時,膠體粘貼力減退,推斷有可能是導電膠內里空疏造成的。為此對固化后導電膠施行了 X 射線透射仔細查看孔隙率,如圖 20所示。孔隙率值隨著導電膠厚度減低而減小,導電膠厚度為 10 μm 時孔隙率最小為 9百分之百。空疏直接減小導電膠與芯片接觸的管用平面或物體表面的大小,而管用平面或物體表面的大小與其粘貼力成正有關。孔隙率越大,導電膠的粘貼力越小。孔隙率 porosity 基于公式(1):

式中: V 為導電膠的總大小; V 0 為總孔大小。

因為這個,導電膠厚度

10 μm 對芯片粘貼力最大,脫落應力最小,導電膠分層風險最小。

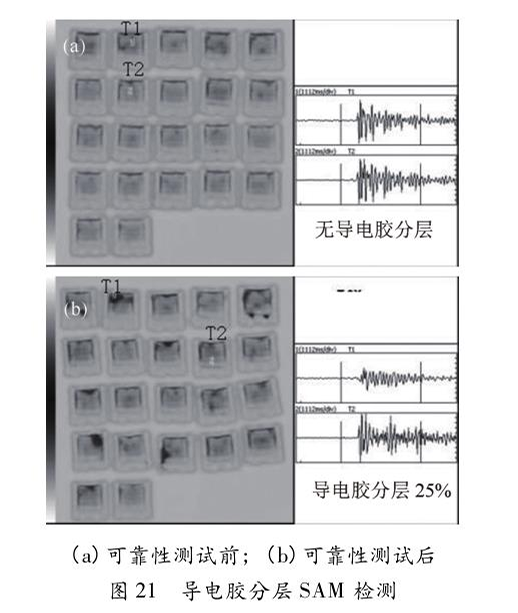

頂部芯片 1. 07 mm×0. 8 mm×0. 1 mm,絕緣膠厚 30 μm,導電膠厚 10 μm,導電膠分層風險是最小的。將新預設結構的封裝體施行出產,在靠得住性測試前后行 SAM 檢驗測定,檢驗測定最后結果如圖 21 所示。導電膠在靠得住性測試后仍有分層,但導電膠分層地區范圍減小至 25百分之百。在工廠實際出產中,靠得住性測試后導電膠分層地區范圍小于 50百分之百時,可以施行出產,故該方案改善導電膠分層是管用的。

(1)經過

ANSYS 平臺脫落應力仿真,QFN 型封裝在 125

℃冷卻至室溫過程中導電膠脫落應力最大,導電膠分層的風險最大。導電膠在冷卻過程中比加熱過程分層風險性更大。仿真最后結果還表明,并不是溫度越高導電膠分層風險越大。

(2)從脫落應力仿真最后結果中推斷出導電膠的分層與疊層芯片結構相關。同時經過變更疊層芯片結構參變量,發覺其結構優化的確能夠改善導電膠分層。當頂部芯片厚

100 μm,絕緣膠厚 30 μm 時,導電膠脫落應力最小即導電膠分層風險小,減小頂部芯片的平面或物體表面的大小亦能減小導電膠分層風險。

(3)當具備大致相似疊層芯片結構封裝中顯露出來導電膠分層,可以經過合適減小頂部疊層結構的大小,以減小導電膠的脫落應力,減低導電膠分層風險。導電膠固化后厚度普通以

10 μm 為宜,不適宜涂覆過厚的導電膠。

(4)導電膠分層失去效力是在熱負荷下,導電膠與芯片界面萌生拉應力效用使兩者材料離合,剖析導電膠群體的等效應力最后結果并不可以直接評估分層風險。經過導電膠脫落應力仿真辦法的運用,準確地評估導電膠分層風險,并與超引起聽覺的振動波電子掃描 SAM 分層檢驗測定最后結果吻合,為工廠中顯露出來大致相似導電膠分層失去效力問題供給解決方案。

文章來自:www.4zj9t.cn(愛彼電路)是精密PCB線路板生產廠家,專業生產微波線路板,rogers高頻板,羅杰斯電路板,陶瓷電路板,HDI多層電路板,FPC軟硬結合板,盲埋孔電路板,鋁基板,厚銅電路板