在半導(dǎo)體芯片的批量生產(chǎn)中,ATE 測試板是連接自動測試設(shè)備(ATE)與被測器件(DUT)的關(guān)鍵載體,其性能直接決定了芯片良率判定的準(zhǔn)確性。本文結(jié)合行業(yè)前沿技術(shù)與公開技術(shù)白皮書,深度解析 ATE 測試板的材料選型、結(jié)構(gòu)設(shè)計及可靠性優(yōu)化方案,揭秘如何通過精密制造實現(xiàn) 0.1% 以下的測試誤判率,為芯片設(shè)計、制造企業(yè)提供技術(shù)參考。

一、ATE 測試板的技術(shù)原理與核心價值

一、ATE 測試板的技術(shù)原理與核心價值

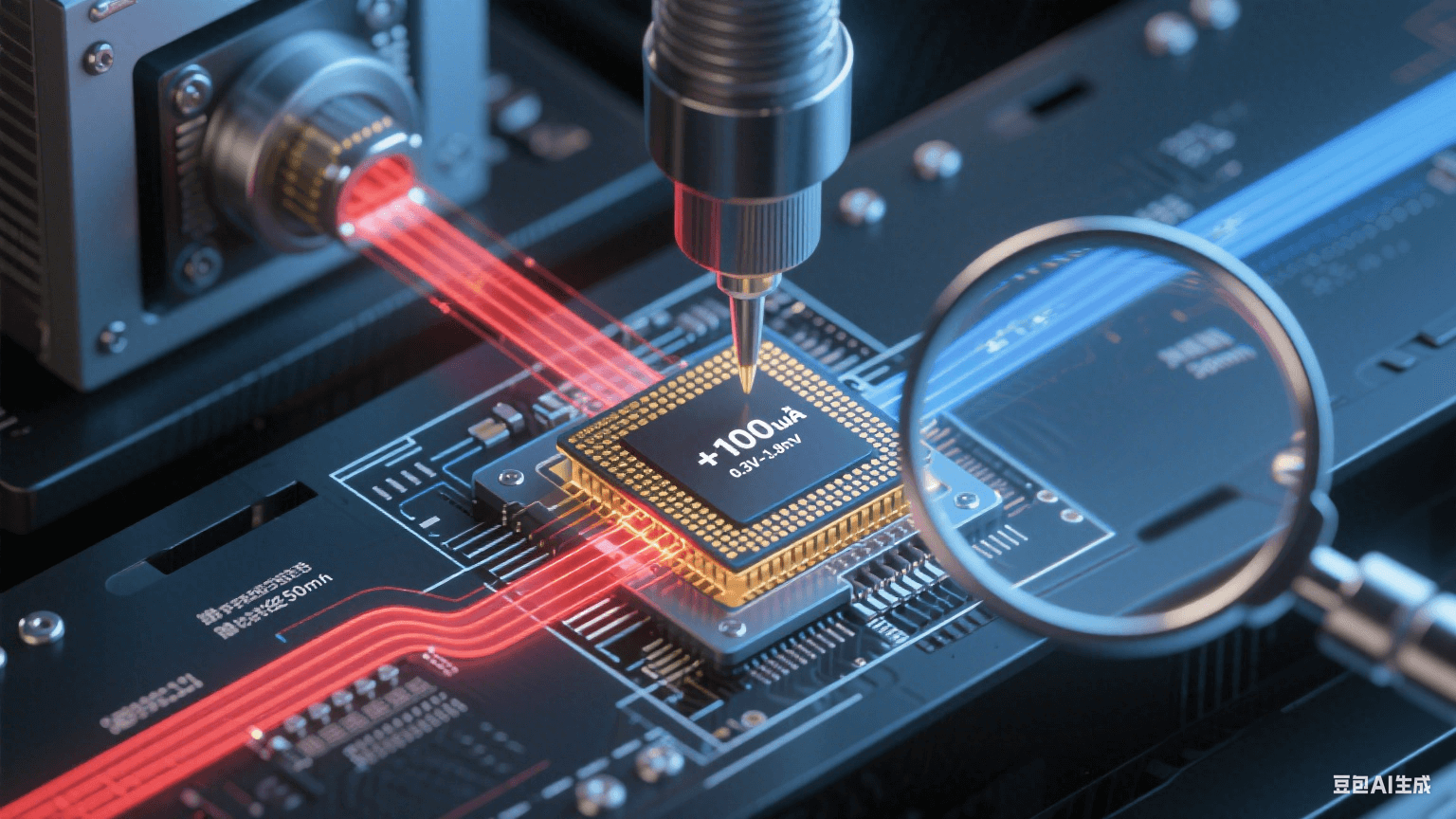

ATE 測試板的核心功能是實現(xiàn)測試機(jī)與芯片之間的信號精準(zhǔn)傳遞。其工作原理可簡化為 “激勵輸入 - 響應(yīng)輸出 - 對比判定” 的閉環(huán)流程。測試機(jī)通過 ATE 測試板向芯片施加特定電信號(如直流電壓、脈沖序列),同時采集芯片的輸出響應(yīng),與預(yù)設(shè)標(biāo)準(zhǔn)值對比后判定芯片是否合格。例如,在檢測芯片 Pin 腳保護(hù)二極管時,需通過 ATE 測試板注入 ±100μA 電流,并測量電壓是否在 0.3V~0.8V 范圍內(nèi)。

這種信號傳輸對測試板的電氣性能提出嚴(yán)苛要求:接觸電阻需≤50mΩ 以避免信號衰減,絕緣阻抗需≥10GΩ 以防止串?dāng)_,同時需支持最高 50GHz 的高頻信號傳輸。

根據(jù)測試階段不同,ATE 測試板可分為晶圓測試(CP)用探針卡和封裝測試(FT)用負(fù)載板。前者需在微米級間距下實現(xiàn)探針與芯片焊盤的可靠接觸,后者則需適配多種封裝形式(如 QFN、BGA)的機(jī)械接口。

兩類測試板共同面臨的挑戰(zhàn)包括:

熱管理:高密度測試時,探針接觸點溫升可達(dá) 15℃以上,可能導(dǎo)致芯片參數(shù)漂移;

信號完整性:在 10GHz 以上頻率下,傳輸線阻抗偏差需控制在 ±5% 以內(nèi),否則會引發(fā)反射和失真;

機(jī)械精度:探針卡的平面度需≤±2μm,以避免彈坑效應(yīng)損壞晶圓。

二、核心組件的選型與設(shè)計要點

二、核心組件的選型與設(shè)計要點

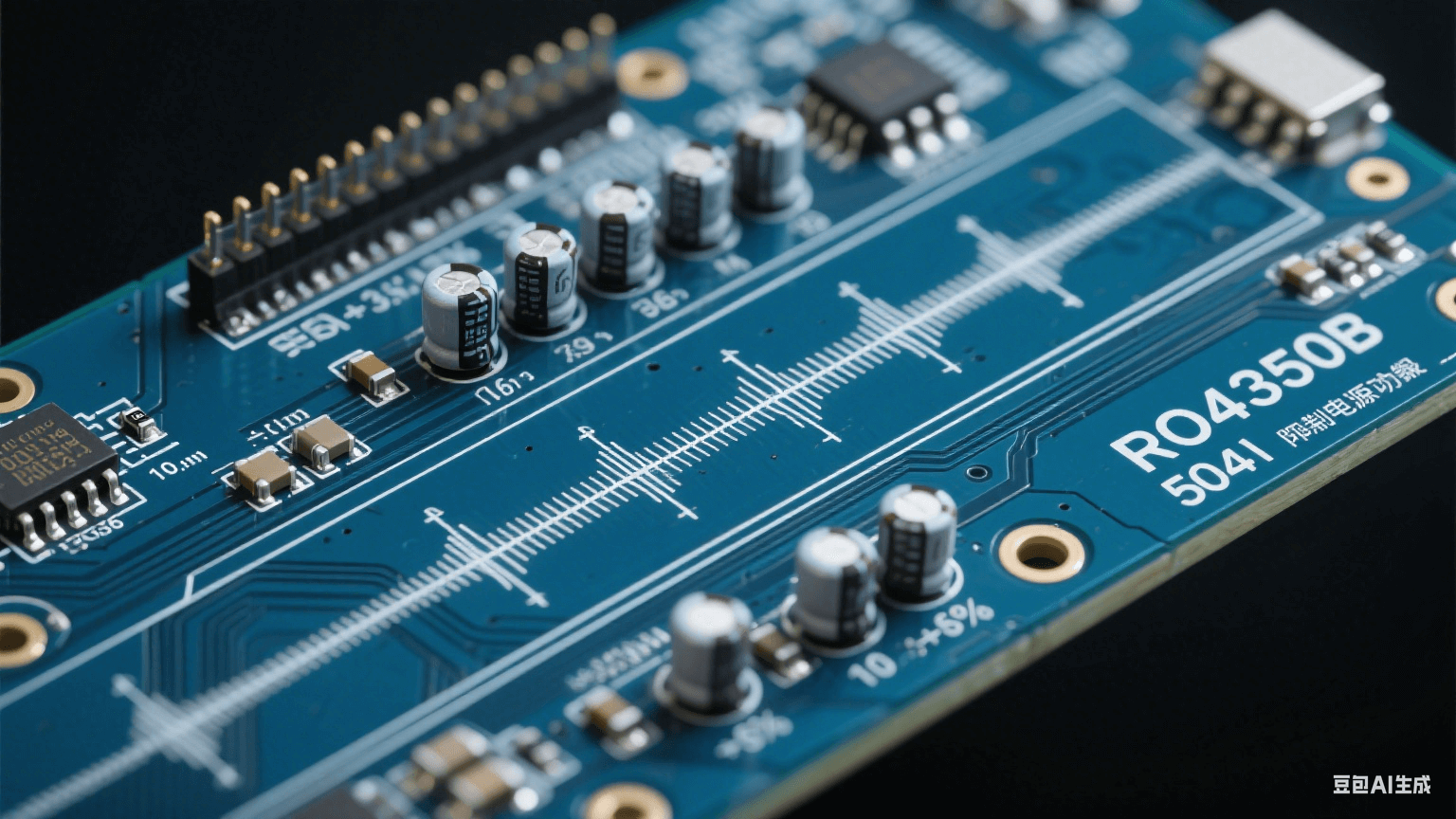

ATE 測試板通常采用高頻高速材料,如 RO4350B(介電常數(shù) 3.66@10GHz)或 EM-827(介電損耗 0.002@10GHz)。這類材料的選擇需平衡以下參數(shù):

介電特性:低介電常數(shù)可減少信號延遲,低損耗因子可降低高頻下的能量衰減;

熱膨脹系數(shù)(CTE):需與探針卡框架材料(如殷鋼)匹配,避免熱應(yīng)力導(dǎo)致結(jié)構(gòu)變形;

機(jī)械強(qiáng)度:20 層以上的多層板需承受≥50N 的探針接觸力而不發(fā)生分層。

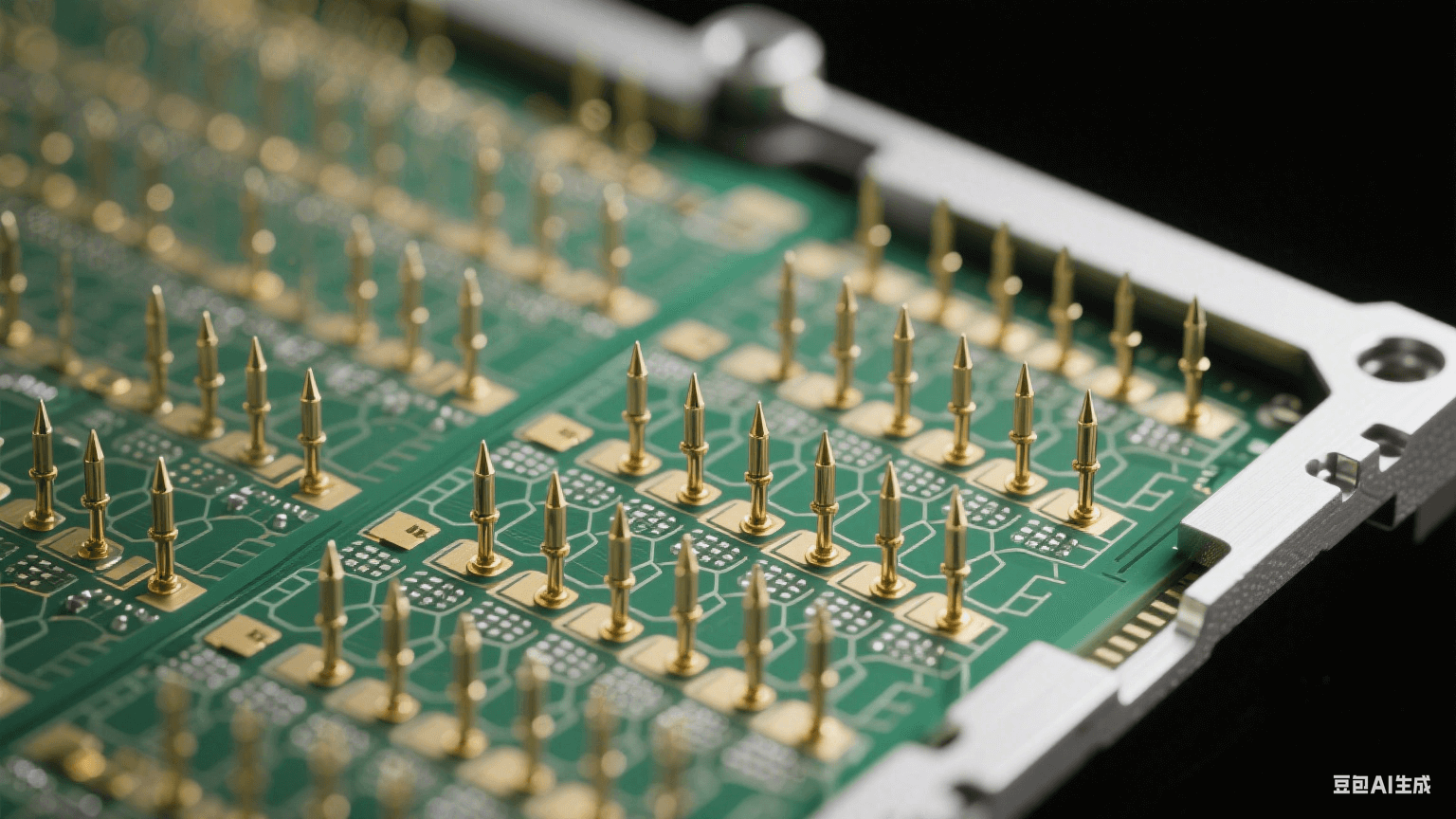

探針卡與測試板的協(xié)同設(shè)計是確保測試精度的關(guān)鍵。行業(yè)實踐表明,當(dāng)探針接觸力控制在 8-12gf、針尖曲率半徑≤5μm 時,測試板的探針壽命可達(dá) 8 萬次以上,較常規(guī)參數(shù)(15gf 接觸力、10μm 曲率半徑)提升 50%。

為實現(xiàn)這一目標(biāo),需遵循以下原則:

探針陣列布局優(yōu)化:采用交錯排列或蜂窩結(jié)構(gòu),可將信號通道密度提升 30%,同時減少相鄰探針的電磁干擾;

焊盤表面處理:鍍金層厚度需≥3μm,且粗糙度 Ra≤0.1μm,以降低接觸電阻并防止氧化;

應(yīng)力釋放設(shè)計:在探針密集區(qū)域增加應(yīng)力緩沖層(如聚酰亞胺薄膜),可將探針斷裂風(fēng)險降低 60%。

高頻測試板需采用多層差分對設(shè)計,例如:

阻抗控制:50Ω 微帶線的線寬公差需≤±5%,蝕刻深度公差≤±2μm;

層間對準(zhǔn):內(nèi)層圖形與外層圖形的偏移需≤±10μm,否則會導(dǎo)致信號傳輸延遲不一致;

去耦設(shè)計:每 10 個信號引腳需配置 1 個 0.1μF 的高頻陶瓷電容,以抑制電源噪聲。

三、測試流程優(yōu)化與質(zhì)量控制

三、測試流程優(yōu)化與質(zhì)量控制

ATE 測試板的校準(zhǔn)分為三個階段:

開路 / 短路校準(zhǔn):通過標(biāo)準(zhǔn)件消除測試板本身的寄生參數(shù)影響;

負(fù)載校準(zhǔn):在實際測試負(fù)載下驗證信號傳輸延遲和損耗;

動態(tài)校準(zhǔn):在測試過程中實時監(jiān)測探針接觸電阻,當(dāng)變化超過 10% 時自動觸發(fā)重新校準(zhǔn)。

這種校準(zhǔn)流程可將測試誤判率從 0.3% 降低至 0.08%,尤其適用于 5G 射頻芯片等高精度測試場景。

為確保測試板的長期穩(wěn)定性,需進(jìn)行以下測試:

溫度循環(huán)測試:在 - 40℃~125℃范圍內(nèi)進(jìn)行 1000 次循環(huán),驗證材料的熱疲勞性能;

振動測試:在 20-2000Hz 頻率下施加 5G 加速度,檢查焊點和機(jī)械結(jié)構(gòu)的可靠性;

壽命測試:通過 10 萬次探針插拔實驗,評估焊盤和探針的磨損程度。

隨著先進(jìn)封裝技術(shù)(如 Chiplet、SiP)的普及,ATE 測試板的通道密度需從當(dāng)前的 2000pin 提升至 5000pin 以上,同時線寬 / 線距需突破 30μm/30μm 的極限。例如,某 3nm 制程晶圓測試板已采用 0.15mm 微孔和 0.05mm 線寬設(shè)計,可支持 1024 個探針的密集排列。

未來 ATE 測試板將集成更多智能功能:

嵌入式傳感器:實時監(jiān)測探針接觸力、溫度等參數(shù),實現(xiàn)異常預(yù)警;

機(jī)器學(xué)習(xí)算法:通過歷史測試數(shù)據(jù)預(yù)測探針磨損趨勢,優(yōu)化測試周期;

自適應(yīng)阻抗匹配:根據(jù)被測芯片的特性自動調(diào)整信號傳輸參數(shù),提升測試效率。

除傳統(tǒng)集成電路測試外,ATE 測試板正逐步滲透至以下領(lǐng)域:

功率半導(dǎo)體:用于 IGBT、SiC MOSFET 等器件的高壓大電流測試,需耐受 1200V 電壓和 200A 電流;

車規(guī)級芯片:滿足 AEC-Q200 標(biāo)準(zhǔn),支持 - 40℃~150℃寬溫環(huán)境下的穩(wěn)定測試;

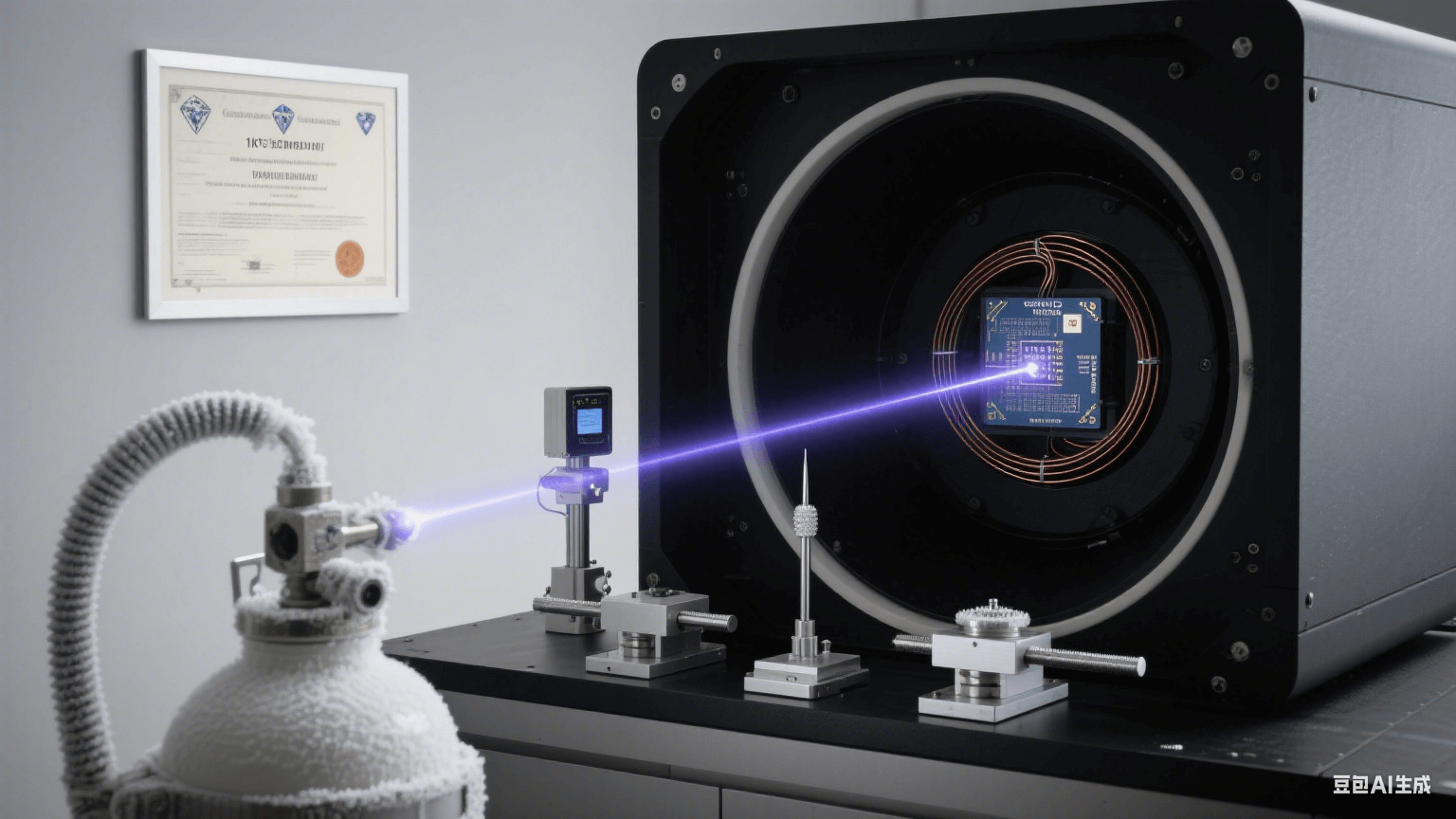

量子芯片:開發(fā)低噪聲、高隔離度的測試板,適配量子比特的超低溫(<1K)測試需求。

從 28nm 到 3nm 制程的演進(jìn),ATE 測試板始終是半導(dǎo)體檢測的 “精度守門人”。隨著半導(dǎo)體產(chǎn)業(yè)向更高性能、更低功耗方向發(fā)展,測試板技術(shù)將持續(xù)突破信號完整性、熱管理和機(jī)械可靠性的邊界。企業(yè)需緊跟行業(yè)趨勢,通過材料創(chuàng)新、結(jié)構(gòu)優(yōu)化和智能化升級,打造適配未來測試需求的高精度載體,為全球半導(dǎo)體產(chǎn)業(yè)鏈的高質(zhì)量發(fā)展提供堅實支撐。