當芯片制程邁入 3nm 時代,IC 封裝基板設(shè)計成為解決信號完整性、熱管理和空間壓縮的關(guān)鍵戰(zhàn)場。通過高密度布線(線寬≤8μm)、異構(gòu)集成和先進散熱結(jié)構(gòu),現(xiàn)代基板在指甲蓋面積內(nèi)承載萬億次數(shù)據(jù)交換,支撐 AI 算力爆發(fā)式增長。

微凸點技術(shù)正重構(gòu)芯片 - 基板互連范式。隨著 Chiplet 架構(gòu)普及,傳統(tǒng)焊球(Bump)間距從 150μm 縮至 40μm,微凸點通過銅柱 + 錫銀合金實現(xiàn) 10μm 級精準對接,阻抗降低 30%,熱循環(huán)壽命提升 5 倍。

痛點:112Gbps 高速信號的趨膚效應(yīng)損耗>15dB/cm

創(chuàng)新方案:

梯度介電層:

graph LR A[頂層LCP εr=2.9] --> B[中層ABF εr=3.3] B --> C[底層陶瓷 εr=5.8] |

電磁屏蔽通道:鉭氮薄膜接地層(厚度 2μm)隔離串擾

性能提升:56GHz 下插入損耗<0.3dB/mm

結(jié)構(gòu) | 傳統(tǒng)設(shè)計 | 優(yōu)化方案 | 改善幅度 |

芯片貼裝區(qū) | 全銅熱沉 | 碳化硅微柱陣列 | 熱阻↓45% |

布線層 | 直線走線 | 分形蛇形走線 | CTE 匹配↑3X |

焊點 | SAC305 焊球 | 銅核焊球 + 納米銀燒結(jié) | 抗疲勞↑8X |

TSV 硅轉(zhuǎn)接板:

通孔直徑 5μm / 深徑比 20:1

銅填充空洞率<0.1%

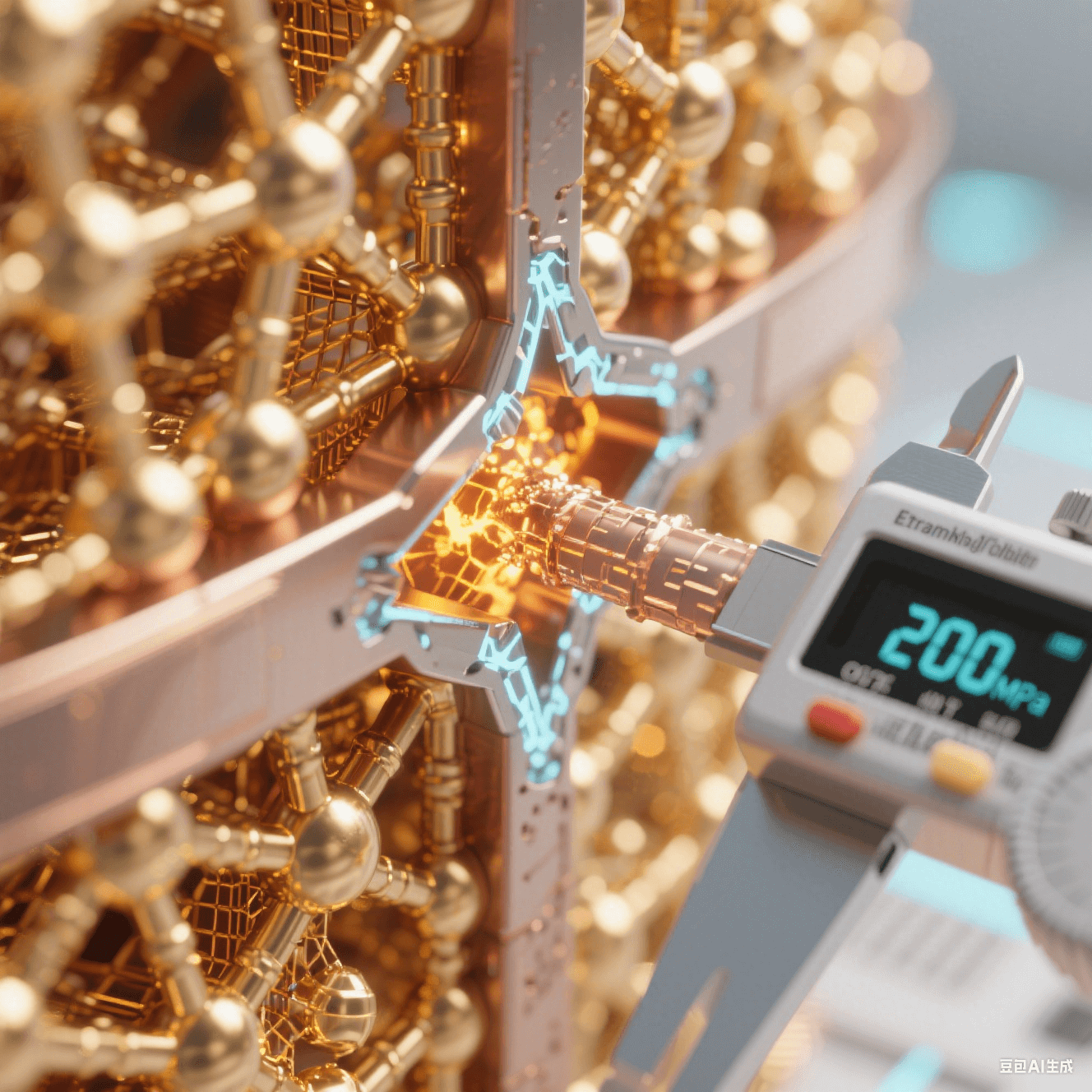

混合鍵合(Hybrid Bonding):

銅 - 銅直接鍵合(間距≤10μm)

界面強度>200MPa

優(yōu)勢:成本 $0.15/cm2,支持 18 層堆疊

局限:熱膨脹系數(shù) 16ppm/℃(芯片 2.6ppm/℃)

適用:手機 APU、中端 GPU

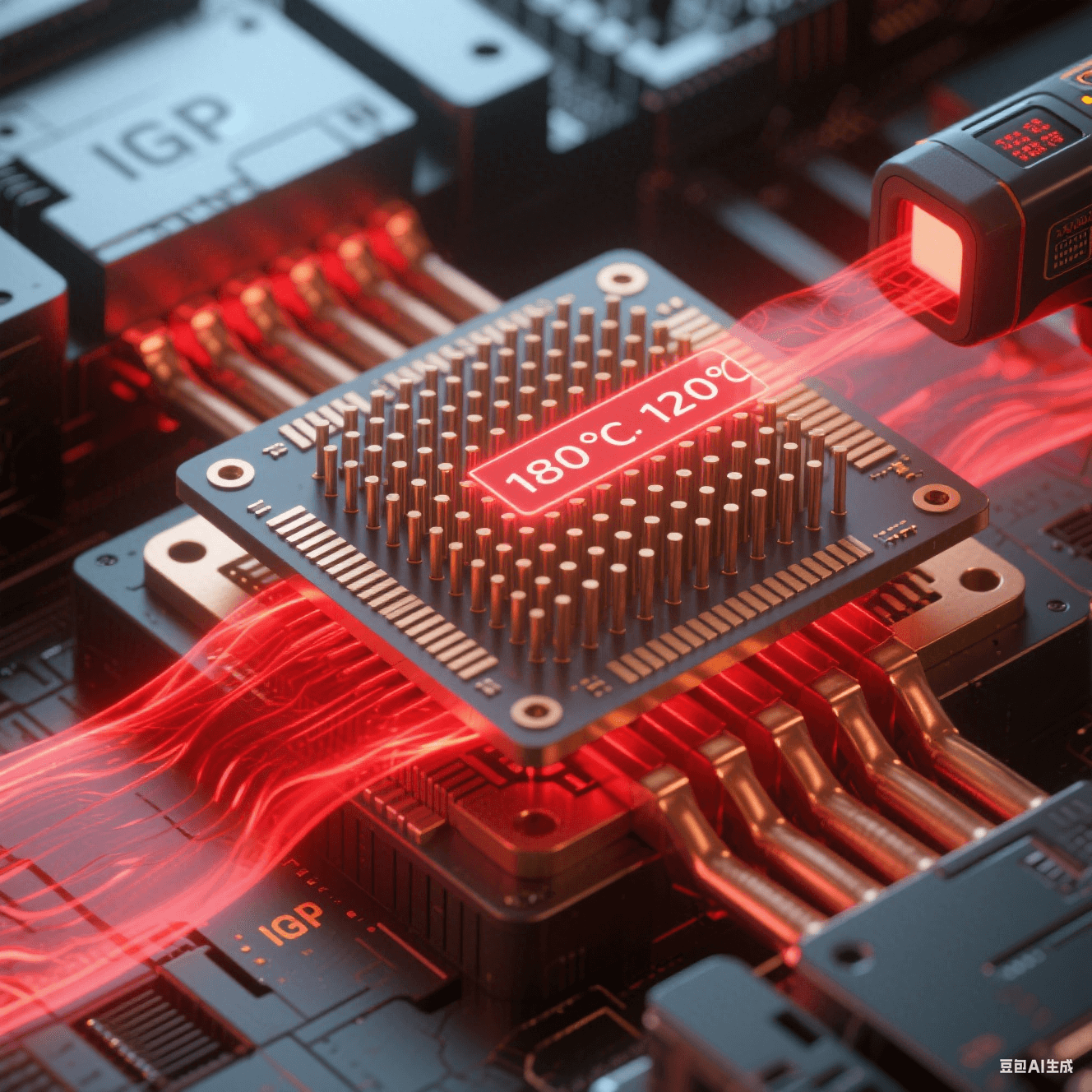

突破:氮化鋁基板(熱導 180W/mK)+ 金導線

場景:激光雷達核心板(耐溫 - 55~200℃)

精密參數(shù):

線寬 / 間距 = 0.8μm/0.8μm

RDL 層厚 3μm±0.1μm

旗艦應(yīng)用:NVIDIA H100 GPU(CoWoS 封裝)

性能亮點:

高頻損耗<0.002dB/GHz

平整度 ±0.5μm(優(yōu)于硅基 ±2μm)

未來方向:蘋果 Vision Pro 微顯示屏驅(qū)動

實時決策:

if 電流密度 > 5e6 A/cm2: 啟用差分對蛇形布線 elif 溫度梯度 > 80℃/mm: 插入熱通孔陣列 |

仿真類型 | 核心指標 | 工具案例 |

電磁場 | S 參數(shù) / 阻抗連續(xù)性 | Ansys HFSS |

熱應(yīng)力 | 翹曲預測 / 焊點疲勞 | Simcenter STAR-CCM+ |

電化學遷移 | 離子擴散速率 | COMSOL Multiphysics |

微孔設(shè)計:盲孔直徑>深度的 0.8 倍

銅厚控制:信號層 18±2μm,電源層 70±5μm

阻焊開窗:比焊盤大 15μm(防焊料橋接)

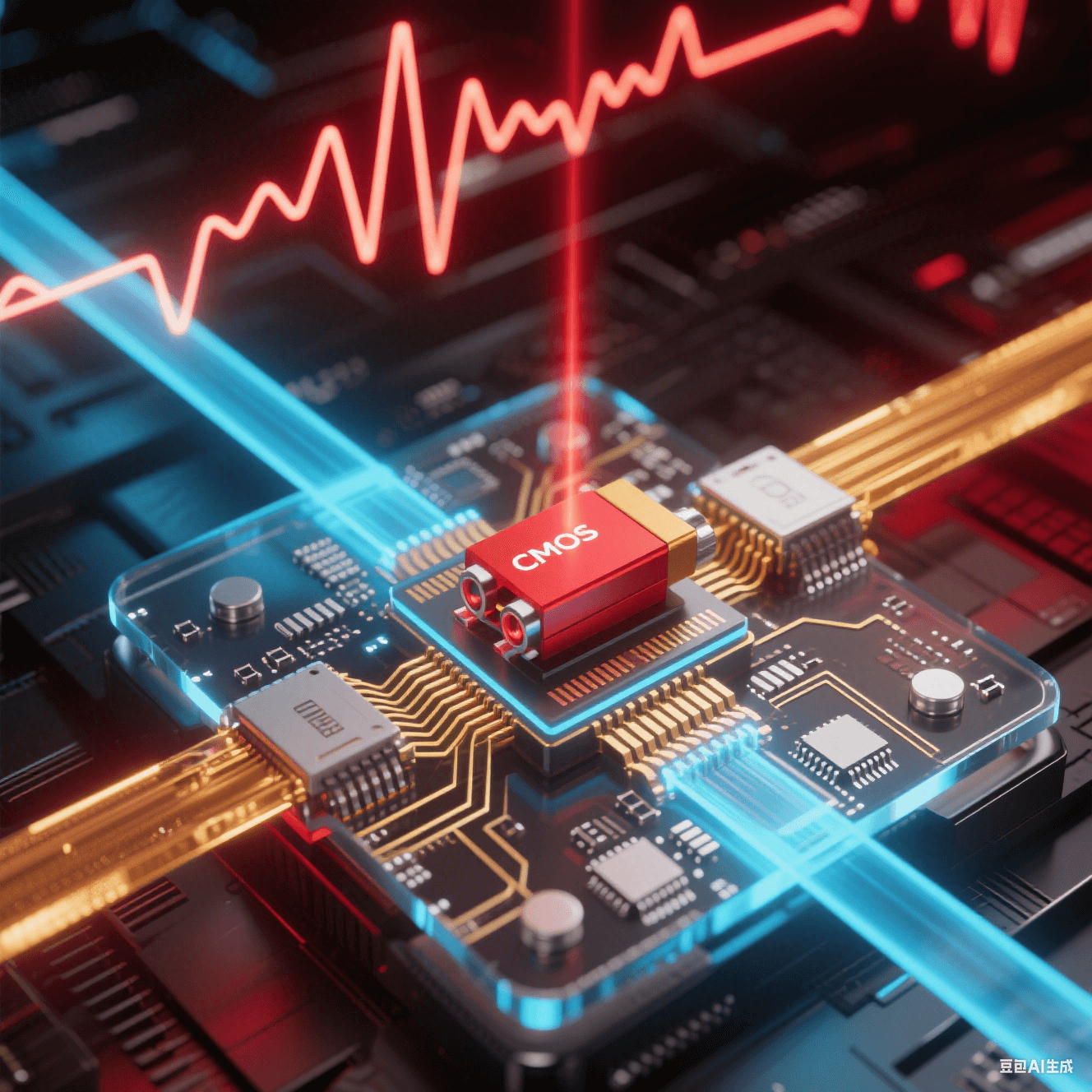

硅光芯片與 CMOS 基板混合集成

波導耦合損耗<0.1dB(當前>1dB)

埋入式 GaN 開關(guān)器件:

開關(guān)頻率>10MHz

功率密度 500W/cm3

超導布線(NbTiN 材料):

77K 溫度下電阻<10??Ω

支持量子比特長程糾纏

IC 封裝基板設(shè)計已從被動連接件進化為主動系統(tǒng)集成平臺。當 3D 異構(gòu)集成突破物理極限,微凸點技術(shù)與硅光融合將催生新一代算力引擎,為 AI、量子計算鋪就高速通路。