隨著電子產品微小型化、多功能化和信號傳輸高頻高速數字化,要求PCB 迅速走向高密度化、高性能化和高可靠性發展。為了適應這個要求,不僅 PCB 迅速走向 HDI BUM板、嵌入(集成)元件 PCB 等,而且 IC 封裝基板已經迅速由無機基板(陶瓷基板)走向有機基板(PCB 板)。有機 IC 封裝基板是在 HDI/BUM板的基礎上繼續‘深化(高密度化)’而發展起來的,或者說 IC 封裝基板是具更高密度化的HDI/BUM板。

1.1 有機封裝基板的提出封裝基板是用于把多個一級(可用二級)封裝IC 組件再封(組)裝形成更大密度與容量的一種基板。由于這類基板的封裝密度很高,因此,其尺寸都不大,大多數為≤50*70mm2。

過去主要是采用陶瓷基板,現在迅速走向高密度PCB封裝基板。

(1)陶瓷封裝基板。

陶瓷封裝基板的應用已有幾十年的歷史了,基優點是CTE 較小,導熱率較高。但是,隨著高密度化、特別是信號傳輸高頻高速數字化的發展,陶瓷封裝基板遇到了嚴厲的挑戰。

① 介電常數 εr 大( 6∽8)。

信號傳輸速度 V 是由來介電常數 εr 決定的,如下式可得知。

V=k ·C/(εr)1/2

其中: k——為常數; C——光速。這就是說,采用較小的介電常數εr,就可以得到較高的信號傳輸速度。還有特性阻抗值等問題。

②密度低。 L/S ≥O.1mm,加上厚度厚、孔徑大,不能滿足IC 高集成度的要求。

③電阻大。大多采用鉬形成的導線,其電阻率(燒結后)比銅大三倍多或更大,發熱量大和影響電氣性能。

④基板尺寸不能大,影響密度和容量提高。由于陶瓷基板的脆性大,不僅尺寸不能大,而且生產、組裝和應用等都要格外小心。

⑤薄型化困難。厚度較厚,大多數為1mm以上。

⑥成本高。

(2)有機( PCB)基板。

有機( PCB)基板,剛好與陶瓷封裝基板相反。

①介電常數 ε r 小(可選擇性大,大多用3∽ 4 的材料)。

②高密度化好。 L/S 可達到 20∽50μm,介質層薄,孔徑小。

③電阻小。發熱低,電氣性能好。

④基板尺寸可擴大。大多數為≤70*100mm2。

⑤可薄型化,目前,雙面/ 四層板,可達到100∽300μm。

⑥成本低。

在 1991 年,由日本野洲研究所開發的用于樹脂密封的倒芯片安裝和倒芯片鍵合(連接)的 PCB 和 HDI/BUM 板,這些有機封裝基板和HDI/BUM 板等比陶瓷基板有更優越的的有利因素和條件,使它作為IC 的裸芯片封裝用基板是非常合適的,特別是用于倒芯片(FC)的金屬絲的封裝上,既解決了封裝的CTE 匹配問題,又解決了高密度芯片的安裝的可行性問題。

關于 PCB 基板的 CTE 較大和導熱差方面,可以通過改進和選擇CCL 基材得到較好的解決。

1.2 IC 封裝基板的類型

1.2.1 IC封裝基板主要的兩個問題。

( 1)搭載裸芯片的封裝基板與所要封裝元(組)件的CTE(熱膨脹系數)匹配(兼容)。

( 2)搭載裸芯片的封裝基板的高密度化,要滿足裸芯片的高集成度要求。

1.2.2 封裝基板的三種類型。

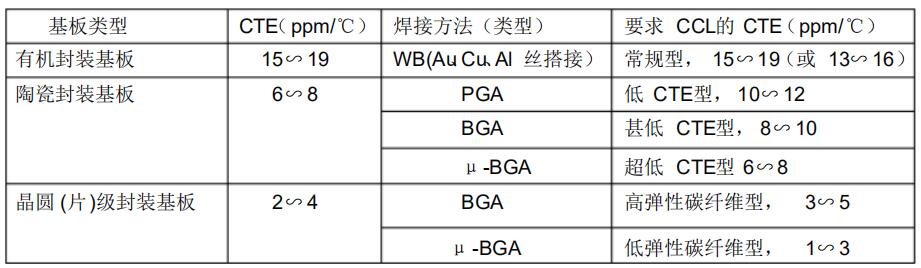

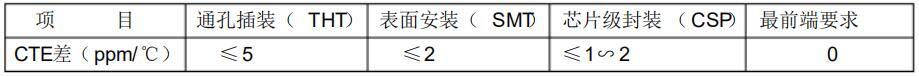

到目前為止,用于裸芯片的封裝基板有三種類型,如表1 和圖 1 所示。

從本質上來說, PCB 是為元(組)件提供電氣互連和機械(物理)支撐的。在今天的電子封裝市場上,主要存在著三種類型的的封裝:

( 1)有機基板的封裝, 其 CTE 為 13∽19ppm/℃,采用金屬絲鍵合 (WB),然后,再 BGA/μBGA焊接到 PCB板上;

( 2)陶瓷基板封裝, 其 CTE 為 6∽8ppm/℃,由于陶瓷基板的缺點, 逐步采用 6∽8ppm/℃有機封裝基板;

( 3)與晶圓片匹配的有機封裝。既理想的尺寸與速度(即芯片級)匹配的封裝,如采用

特別低的 CTE封裝基板與晶圓 (片)級封裝( WLP,wafer level package)、直接芯片安裝 ( DDA ,direct die attach)匹配的安裝 ,其 CTE 接近 2∽4ppm/℃(參見表 1)。

很顯然,常規的PCB是不具備這些高級封裝(低CTE場合)能力的,因此, PCB工業必須發展低 CTE材料,以滿足這些高級封裝基板材料的技術和產品。

表1 三種封裝基板的CTE及對CCL的CTE要求

注:陶瓷封裝基板對CCL要求是指‘裸芯片’已封裝在陶瓷基板,然后再安裝到 PCB基板上而言。

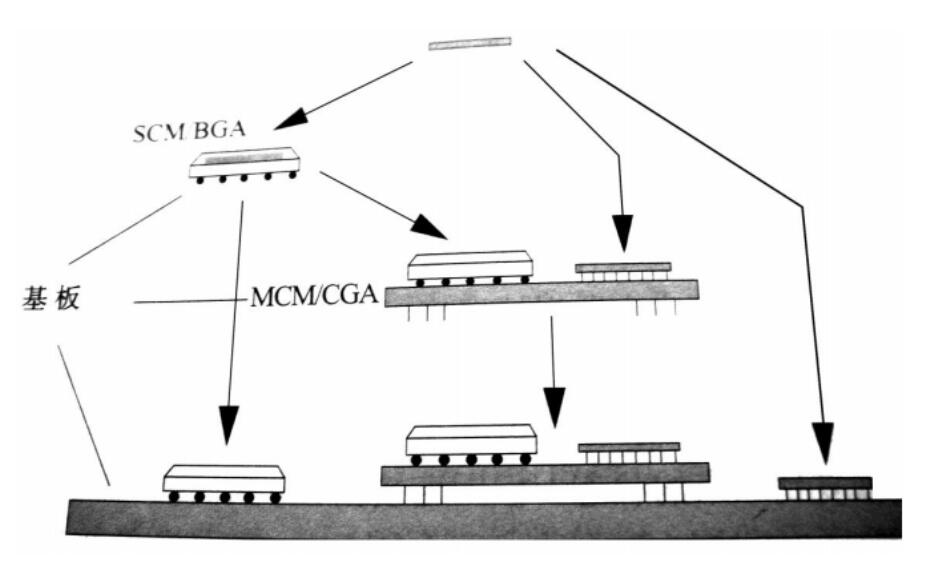

目前,按元(組)件封裝到 封裝基板 上的 CTE大小,可把封裝基板分為三種類型(如圖4 所示)。

圖1 三級基板的示意圖

1.2.3 基板封裝與元(組)件的 CTE 要求。

封裝基板與封裝元(組)件之間的 CTE匹配(兼容)問題。兩者的CTE不匹配或相差甚大(如過去要求≤5ppm/℃,現在要求更高)時,焊接封裝后產生的內應力便威脅著電子產品使用的可靠性和壽命。因此,封裝基板 與所封裝元(組)件之間的CTE匹配(兼容)問題,正隨著安裝高密度化和焊接點面積的縮小而要求兩者的CTE 相差越來越小,即Δ ≤5ppm/℃→ Δ ≤3ppm/℃→ Δ≤2ppm/℃→ Δ ≤1ppm/℃→ Δ =0。如表 2 所示。

表2 封裝基板與所安裝的元件間CTE差的要求是隨著安裝技術發展而不同

注: CTE差( ppm/℃)是指 封裝基板 與所封裝元(組)件之間的 CTE(差別)匹配度。

陶瓷基板封裝是把芯片( die,系指裸芯片)安裝到陶瓷基板上,然后,它可以安裝到PCB基板上。首先,把硅芯片(silicon die )安裝到陶瓷基板(CTE 為 6∽8ppm/℃)上,但是還不能安置到 PCB基板上,因為

PCB的 CTE大小為 16∽19ppm/℃,兩者的 CTE不匹配、差別太大。為了解決這個問題:

①大多采用圓柱形插裝(column instead of balls)來解決陶瓷基板與PCB基板之間的可靠性連接問題。因為,圓柱形引腳是高而細長的固體圓柱形針(pins ),它可以隨著不同膨脹而擺動, 從而是有理由提供可靠的焊接點的。但是, 目前常規的 BGA焊接已經成為主流,要在每個連接區域除去球形(BGA)連接而改成柱形連接,那是很費時和昂貴成本為代價的,顯然這不是根本的出路。

②最好而根本的辦法,應該是把PCB基板的 CTE=16∽19ppm/℃下降到 8∽10ppm/℃或 6∽8ppm/℃的 CTE。這樣,就可以不必再采用陶瓷基板了。但是,隨著 IC 組件的高集成度化、特別是信號傳輸的高頻化和高速數字化的快速發展,由于陶瓷基板的(相對)介電常數大(εr=6.6 ),介電損耗也大,因此陶瓷封裝基板的應用也受到了限制,特別是在10G以上頻率的信號傳輸與計算,因此,其應用的領域越來越小。

有機基板封裝是把裸芯片( die,系指裸芯片)安裝到很高密度的有機基板上,然后,它再安裝到常規密度的大尺寸PCB基板上。 即把硅芯片 (silicon die )以金屬絲安裝 (如 TSOP,thin small-outline package等)有機基板( CTE 為 13∽19ppm/℃)上,然后再以 BGA安裝到常規密度的大尺寸 PCB基板上,或直接應用到超小型的電子產品中,如表 3 所示。

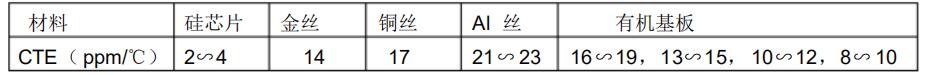

從表 3 可看出:

( 1)典型的芯片的熱膨脹系數 CTE 為 2∽4ppm/℃,這就很難可以直接封裝在PCB上,因為 PCB的 CTE大小為 16∽19ppm/℃(有的文獻數據為13∽15ppm/℃、 13∽17ppm/℃等,這是由基材所用類型決定著),很難能夠與芯片的CTE與之相匹配;

( 2)采用金屬絲(金的CTE 為 14ppm/℃、銅絲的 CTE為 17 ppm/ ℃、 Al 絲的 CTE為 21∽23ppm/℃)連(焊)接封裝在不同CTE大小的有機基板(如目前大多數的IC 封裝基板)上,然后,再以TSOP(thin small-outline package)的金屬引腳或BGA形式再在 PCB基板上進行安裝,因此,有機封裝基板與PCB 基板之間不存在著嚴重的CTE 不匹配問題。盡管, 采用金屬絲鍵合(連接)的有機基板封裝技術,比起陶瓷基板的封裝已具有很多的優點,目前正在高速發展中。但是,比起倒芯片/FCOB/DDA封裝技術,仍然存在著封裝面積大,連接路線長 會降低信號傳輸速度的,對于很高速的信號傳輸是不理想的,一旦有機封裝

基板的 CTE減少到 2∽4ppm/℃或 3∽5ppm/℃時,才會把目前的有機封裝基板減少下來。

倒芯片類型的元(組)件是具有很低的CTE,大多處在 2∽ 4ppm/℃之間。很顯然,把很低的倒芯片類型的元(組)件安裝到高膨脹系數的PCB 基板上是一個巨大的挑戰,特別是高密度的細小焊盤的焊接,那是關系到焊接點的可靠性問題。很小的倒芯片在傳統的PCB上的安裝可行方法之一是借助于焊接部位不填充方法(underfill),但是,它限制了PCB返工(修)的可能性。因此,要把倒芯片可靠地安裝到PCB板上,必須要求 PCB具有很低的CTE ,目前正在開發碳纖維的CCL基板材料。

①低-彈性模量碳纖維。用得多的是PAN碳纖維。低-彈性模量碳纖維具有接近于-0. 4ppm/℃,當與樹脂結合起來形成的復合材料,其CTE可達到4.5∽6.5ppm/℃。這樣的CTE等級已經可與傳統的IC芯片的CTE(5∽7ppm/℃)嚴密匹配了。

②高-彈性模量碳纖維。正如大家了解的高-彈性模量碳纖維PITCH,其 CTE 也接近 -0. 4 ppm/℃,但當高 -- 彈性模量PITCH 纖維與樹脂形成復合材料時,其CTE 為 1.0 ∽3.0ppm/ ℃。可以應用于那些要求很低

CTE(2∽4ppm/℃)的 IC 芯片相匹配的場合。

總之, IC 封裝基板主要體現在:

(一) 基板材料的 CTE更小或匹配, 即此類 IC 基板的 CTE要明顯的減小,并接近(兼容)芯片引腳的CTE,才能保證可靠性;

(二)直接用于裸芯片(KGD)的封裝,因此要求IC 基板更高密度化;

(三)封裝基板的厚度薄,尺寸很小,大多數小于 70*70mm;(四) 大多選用薄型的低CTE基材,如 PI 材料、超薄玻纖布和碳纖維的CCL材料。

有機封裝基板的工藝技術路線,主要有兩種:

(一)傳統高密度的制造方法;

(二)高密度的 HDI/BUM方法。

2.1 有機封裝基板的主要技術指標

有機封裝基板的主要技術指標如下:

( 1)成品外形尺寸。大多數為70*100mm

( 2)基板層數,目前為2∽4。

( 3)基板厚度, 0.1 ∽0.3mm。

( 4)導線寬度 L/ 間距 S。L/S≤50μm(20∽50μm)。半加成法 L/S≥40μm。全加成法 L/S≤40μm(如 5μm)。

( 5)孔徑 Φ為 50∽80μm。

2.2 CCL 材料

根據封裝基板的組裝要求和條件來選擇,因此要充分了解上、 下游的技術指標性能與要求。如,采用 Cu 或 Au絲連接(鍵合)的封裝基板,應該采用對溫度(包括高溫焊接的耐熱)尺寸穩定性,關鍵是翹曲度問題,或CTE匹配問題。

( 1)CTE小、 Tg高的材料。如 BT 材料、 PI 材料、改性 / 高 Tg 環氧材料等。

( 2)薄型基材。即薄型玻纖布所形成的CCL。如 0.1 ∽0.3mm。

2.3 微小孔的形成

( 1)鉆 / 蝕孔。主要有機械鉆孔和激光蝕孔。

①機械鉆孔。采用高速鉆機,轉速為20∽ 30 萬轉 / 分,可達到 Φ50∽80μm

② 激光蝕孔。

(一)紅外( UV)激光蝕孔,光波長( 9.6 μm/10.6μm)孔的厚 / 徑比受到限制(應≤ 0.5 ,否則,問題多) ,現在已經可提供LG—PP 材料。 RCC材料有缺點,介質厚度難保證(特別是均勻性) 。

(二)紫外( UV)激光,可不開‘窗口’ ,提高位置度,光波短(大多采用 0.365μm),孔徑可更小。功率較低,生產率較低。目前已經提高到6∽8 瓦,這個問題已得到解決。

( 2)孔化 / 電鍍。

采用常規孔金屬化工藝和電鍍銅填孔技術是可以完成的

2.4 圖形轉移技術

( 1)L/S 微小化。減少側蝕和提高精細度:

①圖形電鍍(含填孔鍍) ,解決均勻性電鍍,然后蝕刻。

②銅箔減薄(≤ 6μm),然后圖形電鍍(含填孔鍍)/ 或全板鍍,蝕刻形成。

③ 在介質是完成孔金屬化和電鍍(含填孔),然后蝕刻。

( 2)曝光掩膜

①常規菲林。不適宜,不能滿足尺寸精細堵要求。

②玻璃底片。不適宜操作。

③鉻片。適宜。

( 1)蝕刻抗蝕劑。

①干膜。厚度應選≤ 25μm( 80∽120mj/cm2)。

②采用激光直接成像用干膜(8∽12mj/cm2)。

( 4)激光直接刻像。注意保證介質層厚度。

2.5 表面涂(鍍)覆一般情況下,表面涂(鍍)覆層大多數采用化學鍍鎳/ 浸金,現在也可是采用化學鍍銀。當然,采用化學(或電鍍)鎳/ 金/ 鈀,更好。

①化學鍍鎳 / 浸金。金層要厚,并屬軟金,其厚度應≥0.15 μm 或更厚,因為金絲是鍵合(焊接)在金層上的。如果采用銅絲鍵合(焊接)是可以用薄金的。

②化學鍍銀。銀是可以與金、銅絲鍵合(焊接),但銀的厚度要厚些,應≥ 0.30 μm。而化學鍍銀是不能與Al 絲鍵合(焊接)的。